# **Product Specification**

# Part Number: FDS20x2(116x37)TBP

| <b>Revision:</b> | Ver 1.0   |

|------------------|-----------|

|                  |           |

| Issue Date:      | 3/29/2014 |

| Approved By | Review By        | <b>Prepared By</b> |

|-------------|------------------|--------------------|

|             |                  |                    |

|             |                  |                    |

|             |                  |                    |

|             | Control 🗌 Yes    |                    |

|             | Document 🗌 No    |                    |

|             |                  |                    |

|             | Confidential Yes |                    |

|             | Document 🗌 No    |                    |

|             |                  |                    |

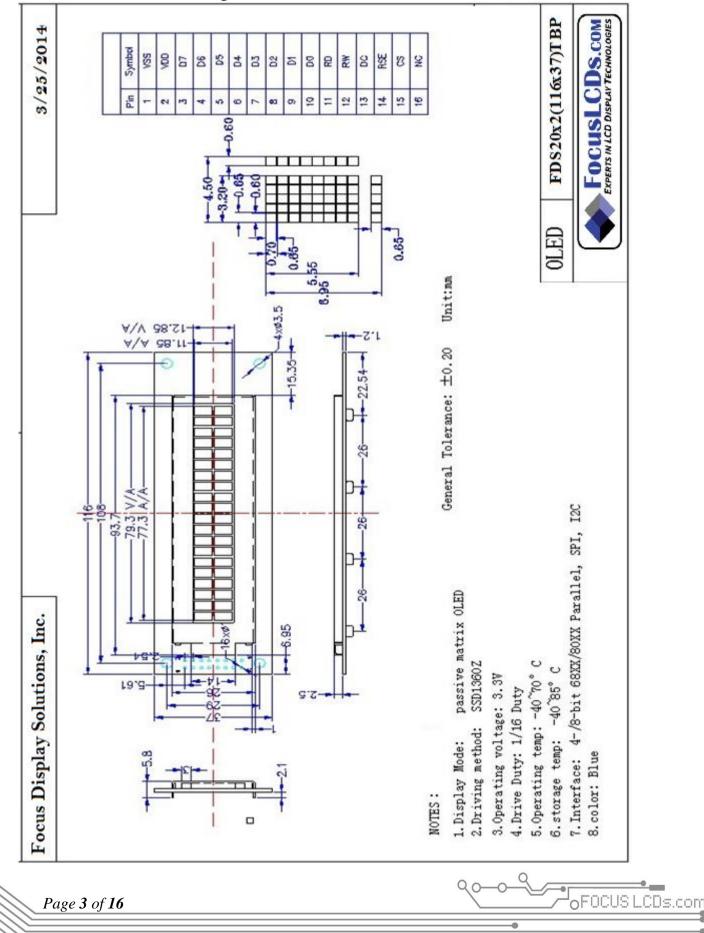

## **1.Module Basic Specification**

- **1.1 Display Specifications**

- 1) Display Mode: Passive Matrix OLED

- 2) Display Color: White

- 3) Drive Duty: 1/16 Duty

- 4) Controller Driver: SSD1360Z

#### 1.2 Module Features

| Items             | Specification                      | Unit |

|-------------------|------------------------------------|------|

| Diagonal A/A Size | 3.05                               | Inch |

| Number of dots    | 20 Characters ( 5x8 dots )x2 Lines | dot  |

| Module size       | 116 x 37 x 5.8                     | mm   |

| Active Area       | 77.3 x 11.85                       | mm   |

| viewing Area      | 79.3 x 12.85                       | mm   |

| Character Pitch   | 3.9 x 6.3                          | mm   |

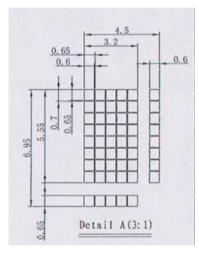

| Character Size    | 3.2 x 5.55                         | mm   |

| Dot Pitch         | 0.65 x 0.70                        | mm   |

| Dot Size          | 0.60x 0.65                         | mm   |

| General Tolerance | $\pm 0.20$                         | mm   |

## 1.3 Mechanical Drawing

-

# 1.4 - Active Area / Address Mapping & Character Construction

|       | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| LINE1 | 04h | 05h | 06h | 07h | 08h | 09h | 0Ah | 0Bh | 0Ch | 0Dh | 0Eh | 0Fh | 10h |

| LINE2 | 44h | 45h | 46h | 47h | 48h | 49h | 4Ah | 4Bh | 4Ch | 4Dh | 4Eh | 4Fh | 50h |

|       | 14  | 15  | 16  | 17  | 18  | 19  | 20  |

|-------|-----|-----|-----|-----|-----|-----|-----|

| LINE1 | 11h | 12h | 13h | 14h | 15h | 16h | 17h |

| LINE2 | 51h | 52h | 53h | 54h | 55h | 56h | 57h |

**FOCUSLCDS.COM** EXPERTS IN LCD DISPLAY TECHNOLOGIES

## 1.5 Pin Definition

| Pin number | Symbol | Туре | Function                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VSS    | Р    | Power supply ground                                                                                                                                                                                                                                                                                                                                                               |

| 2          | VDD    | Р    | 3.3V power supply                                                                                                                                                                                                                                                                                                                                                                 |

| 3~10       | D7~D0  | I/O  | These are 8-bit bi-directional data bus to be connected to<br>the microprocessor's data bus. When serial mode is<br>selected, D1 will be the serial data input SDIN and D0<br>will be the serial clock input SCLK.When I2C mode is<br>selected, D2 & D1 should be tired together and serve as<br>SDA-out & SDA-in in application and D0 is the serial<br>clock input SCL.         |

| 11         | RD     | Ι    | When interface to a 6800-series microprocessor, this pin<br>will be used as the Enable (E) signal, When interface to<br>an 8080-microprocessor, this pin receives the<br>Read(RD#)signal.                                                                                                                                                                                         |

| 12         | RW     | Ι    | This is read/write control input pin connecting to the<br>MCU interface. When interface to a 6800-series<br>microprocessor, Read mode will be carried out when this<br>pin is pulled HIGH and write mode when low .When<br>interface to an 8080-microprocessor, this pin will be the<br>data Write input. When serial interface is selected, this<br>pin must be connected to Vss |

| 13         | DC     | Ι    | This is DATA/COMMAND control pin. When it is<br>pulled HIGH, the data at $D[0~7]$ is treated as data. When<br>it is pulled LOW, the data at $D[0~7]$ will be transferred<br>to the command register. For detail relationship to MCU<br>interface signals, please refer to the Timing<br>Characteristics Diagrams.                                                                 |

| 14         | RSE    | Ι    | This pin is reset signal input (active LOW)                                                                                                                                                                                                                                                                                                                                       |

| 15         | CS     | Ι    | This pin is chip select input (active LOW)                                                                                                                                                                                                                                                                                                                                        |

#### 1.6 Jump

BS0 /BS1 /BS2:MUC bus interface selection pin.

| BS2 | BS1 | BS0 | Interface           |

|-----|-----|-----|---------------------|

| 0   | 0   | 0   | Serial Interface    |

| 0   | 1   | 0   | I <sup>2</sup> C    |

| 1   | 0   | 0   | 8-bit 6800 parallel |

| 1   | 1   | 0   | 8-bit 6800 parallel |

Notes: "0" connection GND and "1" connection VDD.

SPI and I2C interface version PCB are available

FOCUSI

## 2.Absolute Maximum Ratings

| Parameter                                | Symbol          | Min   | Max | Unit | Notes |

|------------------------------------------|-----------------|-------|-----|------|-------|

| Supply Voltage for logic                 | V <sub>DD</sub> | -0.3  | 3.6 | V    | 1,2   |

| Supply Voltage for display               | $V_{CC}$        | 0     | 13  | V    | 1,2   |

| Operating Temperature                    | Тор             | -40   | 70  | °C   | -     |

| Storage Temperature                      | Тятб            | -40   | 85  | °C   | -     |

| Life time (100cd/m <sup>2</sup> )(white) |                 | 20000 | -   | hour | 3     |

#### Notes1:

All the above voltages are on the basis of "Vss =0V "

#### Notes2:

When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur, also for normal operations, it is desirable to use this module under the conditions according to Section 3."Optics and Electrical Characteristics "If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate.

#### Notes3:

$V_{CC}$  = 7.25V, Ta = 25  $^\circ~$  C, 50% Checkerboard.

Software configuration follows Section 6.4 Initialization. End of lifetime is specified as 50% of initial brightness reached. The average operating lifetime at room temperature is estimated by the accelerated operation at high temperature conditions.

# **3.Optics & Electrical Characteristics**

#### 3.1 Optics Characteristics

| Characteristics    | Symbol          | Conditions | Min          | Тур          | Max          | Unit              |

|--------------------|-----------------|------------|--------------|--------------|--------------|-------------------|

| Brightness         | L <sub>br</sub> | Note4      | 120          | 150          | -            | cd/m <sup>2</sup> |

| C.I.E(White)       | (x)<br>(y)      | C.I.E 1931 | 0.26<br>0.28 | 0.30<br>0.32 | 0.34<br>0.36 |                   |

| Dark Room Contrast | CR              |            | -            | 10,000:1     | -            |                   |

| View Angle         |                 |            | -            | Free         |              | - degree          |

Optical measurement taken at  $V_{DD}$  =2.8V,  $V_{CC}$  =7.25V. Software configuration follows Section 4.4 Initialization.

# 3.2 DC Characteristics

| Characteristics                      | Symbol                 | Conditions                      | Min                   | Тур | Max                   | Unit |

|--------------------------------------|------------------------|---------------------------------|-----------------------|-----|-----------------------|------|

| Cumular Valtage for Logic            | V                      | InternalRegulatorEnable(Output) | -                     | 3.3 | -                     | V    |

| Supply Voltage for Logic             | $V_{DD}$               | InternalRegulatorDisable(Input) | 2.4                   | -   | 3.6                   | V    |

| Supply Voltage for I/O               | V                      | 5V Voltage Mode                 | 4.4                   | -   | 5.5                   | V    |

| Supply Voltage for I/O               | V <sub>DDIO</sub>      | Low Voltage Mode                | 2.4                   | -   | 3.6                   | V    |

| Supply Voltage for<br>Display        | V <sub>CC</sub>        | Note4                           | 7                     | 12  | 12.5                  | V    |

| High Level Input                     | $V_{IH}$               | -                               | $0.8 \times V_{DDIO}$ | -   | V <sub>DDIO</sub>     | V    |

| Low Level Input                      | V <sub>IL</sub>        | -                               | 0                     | -   | $0.2 \times V_{DDIO}$ | V    |

| High Level Output                    | V <sub>OH</sub>        | $I_{OUT}=100\mu A, 3.3 MHz$     | $0.9 \times V_{DDIO}$ | -   | V <sub>DDIO</sub>     | V    |

| Low Level Output                     | V <sub>OL</sub>        | $I_{OUT}=100\mu A, 3.3 MHz$     | 0                     | -   | $0.1 \times V_{DDIO}$ | V    |

| Operating Current for $V_{DD}$       | $I_{DD}$               | -                               | -                     | 180 | 300                   | μA   |

| Operating Currentfor V <sub>CC</sub> | т                      | Note5                           | -                     | 16  | 21                    | mA   |

| (V <sub>CC</sub> Supply Externally)  | I <sub>CC</sub>        | Note6                           | -                     | 27  | 32                    | mA   |

| Sleep Mode Current for               | I <sub>DD,SLEE</sub>   |                                 |                       | 1   | 10                    |      |

| V <sub>DD</sub>                      | Р                      | -                               | -                     | 1   | 10                    | μA   |

| Sleep Mode Current for               | I <sub>CC</sub> , SLEE |                                 | _                     | 2   | 10                    | μΑ   |

| V <sub>CC</sub>                      | Р                      | -                               | -                     | Δ   | 10                    | μΑ   |

Note 4: VDD =2.8V,VCC =12V, 30% Display Area Turn on.

Note 5: VDD =2.8V,VCC =12V, 100% Display Area Turn on.

Software configuration follows Section 4.4 Initialization.

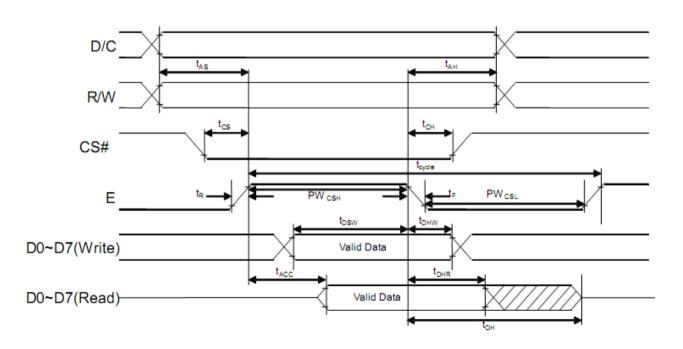

## 3.3 AC Characteristics

3.3.1 68XX-Series MPU Parallel Interface Timing Characteristics:

$(TA=25^{\circ}C, V_{DD} - V_{SS}=1.65V \text{ to } 3.3V)$

| Symbol | Parameter                                  | Min | Туре | Max | Unit |

|--------|--------------------------------------------|-----|------|-----|------|

| tcycle | Clock Cycle Time (write cycle)             | 400 | -    | -   | ns   |

| tas    | Address Setup time                         | 13  | -    | -   | ns   |

| tан    | Address Hold time                          | 17  | -    | -   | ns   |

| tdsw   | Write Data Setup Time                      | 35  | -    | -   | ns   |

| tdhw   | Write Data Hold time                       | 18  | -    | -   | ns   |

| tdhr   | Read Data Hold Time                        | 13  | -    | -   | ns   |

| toн    | Output Disable Time                        | -   | -    | 90  | ns   |

| tacc   | Access Time (RAM)<br>Access Time (command) | -   | -    | 200 | ns   |

| PWcsl  | Chip Select Low Pulse Width (read RAM)     | 250 | -    | -   | ns   |

|        | Chip Select Low Pulse Width (read command) | 250 | -    | -   | ns   |

|        | Chip Select Low Pulse Width (write)        | 50  | -    | -   | ns   |

| РWсsн  | Chip select High Pulse Width (read)        | 155 | -    | -   | ns   |

|        | Chip Select High Pulse Width (write)       | 55  | -    | -   | ns   |

| tr     | Rise Time                                  | -   | -    | 15  | ns   |

| tr     | Fall Time                                  | -   | -    | 15  | ns   |

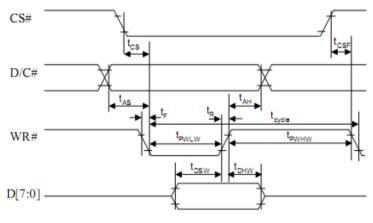

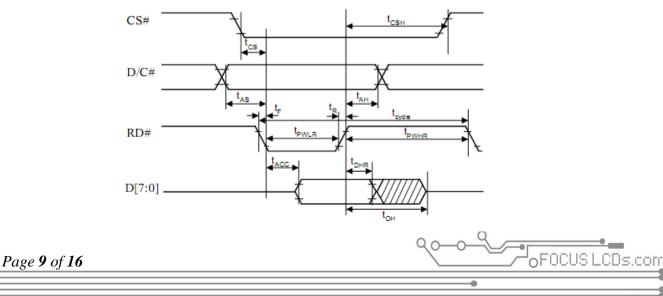

#### 3.3.2 80XX-Series MPU Parallel Interface Timing Characteristics:

$(TA=25^{\circ}C, V_{DD} - V_{SS}=1.65V \text{ to } 3.3V)$

| Symbol        | Parameter                            | Min | Туре | Max | Unit |

|---------------|--------------------------------------|-----|------|-----|------|

| tcycle        | Clock Cycle Time (write cycle)       | 400 | -    | -   | ns   |

| tas           | Address Setup time                   | 13  | -    | -   | ns   |

| tан           | Address Hold time                    | 17  | -    | -   | ns   |

| tcs           | Chip Select time                     | 0   | -    | -   | ns   |

| tсsн          | Chip select Hold Time To read signal | 0   | -    | -   | ns   |

| tcsf          | Chip select hold time                | 0   | -    | -   | ns   |

| tdsw          | Write Data Setup Time                | 35  | -    | -   | ns   |

| tdhw          | Write Data Hold time                 | 18  | -    | -   | ns   |

| tdhr          | Read Data Hold Time                  | 13  | -    | -   | ns   |

| toн           | Output Disable Time                  | -   | -    | 70  | ns   |

| tacc          | Access Time                          | -   | -    | 200 | ns   |

| <b>t</b> PWLR | Read Low time                        | 250 | -    | -   | ns   |

| tpwlw         | Write Low time                       | 50  | -    | -   | ns   |

| <b>t</b> PWHR | Read High time                       | 155 | -    | -   | ns   |

| tpwhw         | Write High time                      | 55  | -    | -   | ns   |

| tr            | Rise Time                            | -   | -    | 15  | ns   |

| tf            | Fall Time                            | -   | -    | 15  | ns   |

#### Write cycle

Read Cycle

# 4. Functional Specification

#### 4.1 Commands

| Command                      | R<br>S | R/<br>W | DB<br>7 | DB<br>6    | DB<br>5 | DB<br>4 | DB<br>3      | DB<br>2      | DB<br>1        | DB<br>0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------------------|--------|---------|---------|------------|---------|---------|--------------|--------------|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Clear                        | 0      | 0       | 0       | 0          | 0       | 0       | 0            | 0            | 0              | 1       | Write "20H" to DDRAM and set DDRAM address to "00H" from AC.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Display<br>Return Home       | 0      | 0       | 0       | 0          | 0       | 0       | 0            | 0            | 1              | X       | Set DDRAM address to "00H", return cursor to its<br>original position, if shifted. The contents of<br>DDRAM are not changed.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Entry Mode<br>Set            | 0      | 0       | 0       | 0          | 0       | 0       | 0            | 1            | I/D            | S       | Assign cursor / blink moving direction with<br>DDRAM address:<br>I/D = "1": cursor/ blink moves to right &<br>DDRAM address is increased by 1 (POR)<br>I/D = "0": cursor/ blink moves to left & DDRAM<br>address is decreased by 1<br>Assign display shift with DDRAM address.<br>S = "1": make display shift of the enabled lines by<br>the DS4 to DS1 bits in the shift enable instruction.<br>Left/ right direction depends on I/D bit selection.<br>S = "0": display shift disable (POR) |  |  |  |  |

| Display<br>ON/OFF<br>Control | 0      | 0       | 0       | 0          | 0       | 0       | 1            | D            | С              | В       | Set display/cursor/blink ON/OFF<br>D = "1": display ON,<br>D = "0": display OFF (POR),<br>C = "1": cursor ON,<br>C = "0": cursor OFF (POR),<br>B = "1": blink ON,<br>B = "0": blink OFF (POR).                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Cursor or<br>Display<br>Shif | 0      | 0       | 0       | 0          | 0       | 1       | S/<br>C      | R/<br>L      | X              | x       | Set cursor moving and display shift control bit, and<br>the direction, without changing DDRAM data.<br>S/C = "1": display shift,<br>S/C = "0": cursor shift,<br>R/L = "1": shift to right,<br>R/L = "0": shift to left                                                                                                                                                                                                                                                                       |  |  |  |  |

| Function set                 | 0      | 0       | 0       | 0          | 1       | D<br>L  | N            | R<br>E       | BR<br>1        | BR<br>0 | Parallel bus width, DL<br>when DL= "1" (POR): 8-bit,<br>when DL = "0": 4-bit<br>Numbers of display line, N<br>when N = "1" (POR): 2-line,<br>when N = "0": 1-line<br>Extension register, RE ("0")<br>Brightness ratio, BR[1:0]<br>(% setting of different contrast level)<br>00: 100%,<br>01: 75%,<br>10: 50%,<br>11: 25%                                                                                                                                                                    |  |  |  |  |

| Set CGRAM<br>address         | 0      | 0       | 0       | 1          | C       |         |              | enera<br>Add | tor (C<br>ress | G)      | Set CGRAM address in address counter.<br>(POR=00 0000)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Set<br>DDRAM<br>Address      | 0      | 0       | 1       | Disj       | play I  |         | DD)<br>or Ac |              | Addro          | ess /   | Set DDRAM address in address counter.<br>(POR=000 0000)                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Write data                   | 1      | 0       |         | Write Data |         |         |              |              |                |         | Write data into internal RAM<br>(DDRAM / CGRAM ).                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Read Data                    | 1      | 1       |         |            |         | Read    | Data         | L            |                |         | Read data from internal RAM<br>(DDRAM / CGRAM ).                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

Page 10 of 16

QO OFOCUS LCDs.com

FOCUSI

#### 4.2 Power down and Power up Sequence

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

- 4.2.1 Power up Sequence:

- 1. Power up  $V_{DD}$

- 2. Send Display off command

- 3. Initialization

- 4. Clear Screen

- 5. Power up  $V_{CC}$

- 6. Delay 100ms (When  $V_{CC}$  is stable)

- 7. Send Display on command

4.2.2 Power down Sequence:

- 1. Send Display off command

- 2. Power down  $V_{CC}$

- 3. Delay 100ms (When  $V_{CC}$  has reach 0 and panel is completely discharged)

- 4. Power down  $V_{DD}$

Note :

- 1) Since an ESD protection circuit is connected between  $V_{DD}$  and  $V_{CC}$  inside the driver IC,  $V_{CC}$  becomes lower than  $V_{DD}$  whenever  $V_{DD}$  is ON and  $V_{CC}$  is OFF.

- 2)  $V_{CC}$  should be kept float (disable) when it is OFF.

- 3) Power Pins ( $V_{DD}$ ,  $V_{CC}$ ) can never be pulled to ground under any circumstance.

- 4)  $V_{DD}$  should not be power down before  $V_{CC}$  power down.

## 4.3 **OLED Init\_IC** Void Init\_IC( )

#### {

| Write_Command(0x01);<br>Write_Command(0x02);<br>Write_Command(0x06);<br>Write_Command(0x0c); | Write_Data(0x20); //Clear Display<br>// Return Home<br>// Entry Mode Set<br>// Display ON /OFF Control |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Write_Command(0xD3);<br>Write_Command(0x00);<br>Write_Command(0x40);                         | <pre>// Set Display Offset // Set Display Start Line</pre>                                             |

| white_Command(0x40),                                                                         | // Set Display Start Line                                                                              |

| Write_Command(0X38);                                                                         | // Function Set                                                                                        |

| Write_Command(0x3c);                                                                         | // Function Set re                                                                                     |

| Write_Command(0x71);<br>Write_Data(0x00);                                                    | // Function Selection A                                                                                |

| Write_Command(0x72);<br>Write_Data(0x04);                                                    | // Function Selection B                                                                                |

| Write_Command(0x79);                                                                         | // OLED characterization                                                                               |

| Write_Command(0x81);<br>Write_Command(0x70);                                                 | // contrast control                                                                                    |

| Write_Command(0xd5);<br>Write_Command(0x80);                                                 | <pre>// display divide ratio/osc. freq. mode // Osc. Freq:360kHz,DivideRation:1</pre>                  |

| Write_Command(0xd9);<br>Write_Command(0x22);                                                 | // set pre-charge period<br>// set period                                                              |

| Write_Command(0xda);<br>Write_Command(0x10);                                                 | // Set SEG Pins Hardware Configuration                                                                 |

| Write_Command(0xDB);<br>Write_Command(0x00);                                                 | // VCOMH deselect level mode                                                                           |

| Write_Command(0xDC);                                                                         | // Set VSL / GPIO                                                                                      |

| Write_Command(0x01);                                                                         | // enanble GPIO                                                                                        |

| Write_Command(0x78); //<br>Write_Command(0x38);                                              | // close SD                                                                                            |

|                                                                                              |                                                                                                        |

}

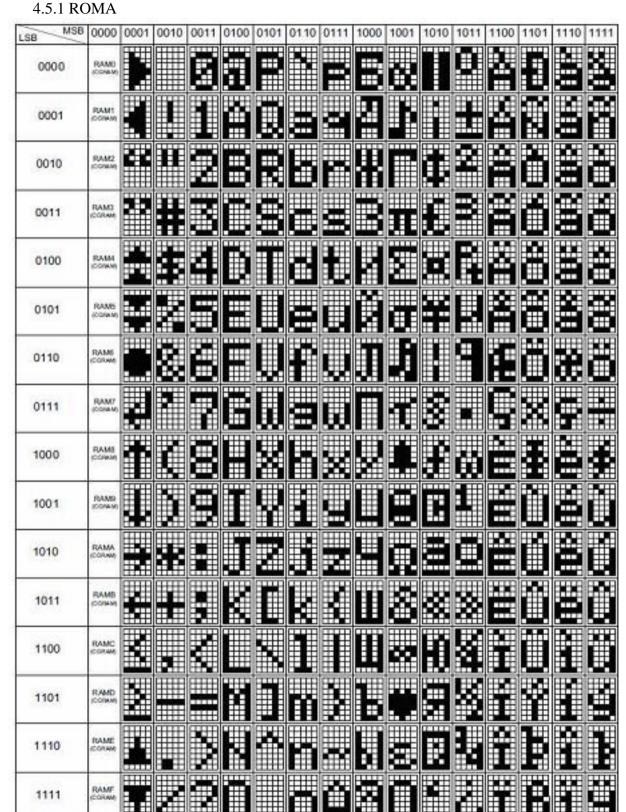

# 4.4 SSD1360Z CGROM Character Code

Page **13** of **16**

C 90 -0 oFOCUS LCDs.com

**FOCUSLCDS.COM** EXPERTS IN LCD DISPLAY TECHNOLOGIES

## TFT | OLED | Character | VATN Bistable | Graphic | Touch Panels Segment | Custom Solutions

#### 4.5.2 RMOB

| LSB  | 0000             | 0001 | 0010  | 0011 | 0100 | 0101 | 0110     | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|------|------------------|------|-------|------|------|------|----------|------|------|------|------|------|------|------|------|------|

| 0000 | RAMO             |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 0001 | RAM1<br>(CORAM)  |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 0010 | RAM2<br>(DGRAW)  |      |       |      |      |      |          | r    |      |      | I    |      |      |      |      |      |

| 0011 | RAM3<br>(conum)  |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 0100 | RAM4<br>(CORM)   |      |       |      |      |      |          | ł,   |      |      |      |      |      |      |      |      |

| 0101 | RAMS<br>(corw)   |      |       |      |      |      |          |      |      |      |      | đ    |      |      |      |      |

| 0110 | RAM6<br>(CORAN)  |      | 8     |      |      |      | ł        |      | Ö    |      |      | T    |      |      |      |      |

| 0111 | RAM7<br>(CORAM)  |      |       |      |      |      |          |      |      | ø    |      |      |      |      |      | Π    |

| 1000 | RAM8<br>(CORAN)  |      |       |      |      |      |          |      |      |      |      |      |      | ļ    |      |      |

| 1001 | RAM9<br>(CORW)   |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 1010 | RAMA<br>(CONAM)  |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 1011 | RAMB<br>(00/1AH) |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 1100 | RAMC             |      |       |      |      |      |          |      |      |      |      |      |      |      | đ    |      |

| 1101 | RAMD<br>(CORM)   |      |       |      |      |      | IL TATES |      |      |      |      |      |      |      |      |      |

| 1110 | RAME<br>(CORAM)  |      | L III |      |      |      |          |      |      |      |      |      |      |      |      |      |

| 1111 | RAMF<br>(CORAM)  |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      |

Page 14 of 16

oFOCUS LCDs.co

#### 4.5.3 ROMC

| SB MSB | 0000            | 0001 | 0010 | 0011 | 0100 | 0101 | 0110              | 0111 | 1000 | 1001              | 1010 | 1011 | 1100 | 1101 | 1110 | 1111  |

|--------|-----------------|------|------|------|------|------|-------------------|------|------|-------------------|------|------|------|------|------|-------|

| 0000   | RAMO<br>(CGRAM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0001   | RAM1<br>(CORAN) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0010   | RAM2<br>(CORMA) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0011   | RAMS<br>(CORAM) |      |      |      |      |      |                   |      |      | Π                 |      |      |      |      |      |       |

| 0100   | RAMA<br>(CORAM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0101   | RAMS<br>(CORAN) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0110   | RAME            |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 0111   | RAM7<br>(CORAM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 1000   | RAMB<br>(CGRIM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 1001   | RAM9<br>(CONAM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 1010   | RAMA<br>(DORAM) |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      |       |

| 1011   | RAMB<br>(CORAM) |      |      |      |      |      |                   |      |      |                   | **   |      |      |      |      |       |

| 1100   | RAMC CORM       |      |      |      | _    |      |                   |      |      |                   |      |      |      |      |      |       |

| 1101   | RAMD<br>(COREM) |      |      |      |      |      | COLUMN TWO IS NOT |      |      | The second second |      |      |      |      |      |       |

| 1110   | RAME<br>(CORAM) |      |      |      |      |      |                   |      |      |                   | R    |      |      |      |      |       |

| 1111   | RAMP<br>(CORM)  |      |      |      |      |      |                   |      |      |                   |      |      |      |      |      | 10000 |

Page **15** of **16**

oFOCUS LCDs.com

- 5. Relibality

- 5.1 Contents of Reliability Tests

| Item                                | Conditions                               | Criteria        |  |  |

|-------------------------------------|------------------------------------------|-----------------|--|--|

| High Temperature Operation          | 70°C, 240 hrs                            |                 |  |  |

| Low Temperature Operation           | -40°C, 240 hrs                           |                 |  |  |

| High Temperature Storage            | 80°C, 240 hrs                            | The operational |  |  |

| Low Temperature Storage             | -40°C, 240 hrs                           | functions work. |  |  |

| High Temperature/Humidity Operation | 60°C, 90% RH, 120 hrs                    |                 |  |  |

| Thermal Shock                       | -40°C ⇔ 85°C, 24 cycles<br>60 mins dwell |                 |  |  |

\* The samples used for the above tests do not include polarizer.

\* No moisture condensation is observed during tests.

#### 5.2 Failure Check Standard

After the completion of the described reliability test, the samples were left at room temperature for 2 hrs prior to conducting the failure test at 23+/-5°C; 55+/-15%RH.

## 6. Outgoing Quality Control Specifications

6.1 Environment Required

Customers test & measurement are required to be conducted under the following conditions:

| $\partial$                                                    |                |

|---------------------------------------------------------------|----------------|

| Temperature:                                                  | 23+/-5°C       |

| Humidity:                                                     | 55 + (-15% RH) |

| Fluorescent Lamp:                                             | 30W            |

| Distance between the Panel & Eyes of the Inspector :          | $\geq$ 50cm    |

| Finger glove (or finger cover) must be worn by the inspector. | $\geq$ 30cm    |

| Inspection table or jig must be anti-electrostatic.           |                |

|                                                               |                |

## 6.2 Sampling Plan

Level II, Normal Inspection, Single Sampling, MIL-STD-105E