# High-Voltage, Current-Mode PWM Controller

#### **Features**

- ▶ 10 to 450V input voltage range

- <1.3mA supply current</p>

- >1.0MHz clock

- >20:1 dynamic range @ 500KHz

- ▶ 49% Maximum duty cycle version

- Low internal noise

### **Applications**

- Off-line high frequency power supplies

- Universal input power supplies

- ► High density power supplies

- Very high efficiency power supplies

- Extra wide load range power supplies

### **General Description**

The Supertex HV9120 is a Switch Mode Power Supply (SMPS) controller subsystem that can start and run directly from almost any DC input, from a 12V battery to a rectified and filtered 240V AC line. It contains all the elements required to build a single-switch converter except for the switch, magnetic assembly, output rectifier(s) and filter(s).

A unique input circuit allows the HV9120 to self-start directly from a high voltage input, and subsequently take the power to operate from one of the outputs of the converter it is controlling, allowing very efficient operation while maintaining input-to-output galvanic isolation limited in voltage only by the insulation system of the associated magnetic assembly. A ±2% internal bandgap reference, internal operational amplifier, very high speed comparator, and output buffer allow production of rugged, high performance, high efficiency power supplies of 50W or more, which can still be over 80% efficient at outputs of 1.0W or less. The wide dynamic range of the controller system allows designs with extremely wide line and load variations with much less difficulty and much higher efficiency than usual. The exceptionally wide input voltage range also allows better usage of energy stored in input dropout capacitors than with other PWM ICs. Remote on/ off controls allow either latching or nonlatching remote shutdown. During shutdown, the power required is under 6.0mW.

For detailed circuit and application information, please refer to application notes AN-H13, AN-H21 to AN-H24.

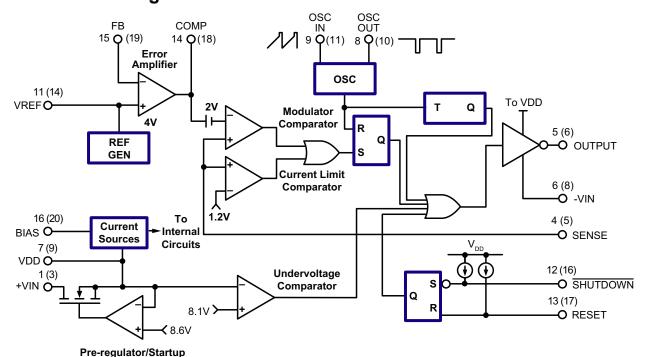

### **Functional Block Diagram**

Note:

Pin numbers in parentheses are for PLCC package.

### **Ordering Information**

| Part Number     | Package Options | Packing   |

|-----------------|-----------------|-----------|

| HV9120NG-G      | 16-Lead SOIC    | 45/Tube   |

| HV9120NG-G M901 | 16-Lead SOIC    | 1000/Reel |

| HV9120NG-G M934 | 16-Lead SOIC    | 2500/Reel |

| HV9120P-G       | 16-Lead PDIP    | 24/Tube   |

| HV9120PJ-G      | 20-Lead PLCC*   | 48/Tube   |

| HV9120PJ-G M910 | 20-Lead PLCC*   | 1000/Reel |

<sup>-</sup>G denotes a lead (Pb)-free / RoHS compliant package

### **Absolute Maximum Ratings**

| Parameter                                                 | Value                          |

|-----------------------------------------------------------|--------------------------------|

| Input voltage, +V <sub>IN</sub>                           | 450V                           |

| Device supply voltage, V <sub>DD</sub>                    | 15.5V                          |

| Logic input voltage                                       | -0.3V to V <sub>DD</sub> +0.3V |

| Linear input voltage                                      | -0.3V to V <sub>DD</sub> +0.3V |

| Pre regulator input current (continuous), I <sub>IN</sub> | 2.5mA                          |

| Operating temperature range                               | -55°C to +125°C                |

| Storage temperature range                                 | -65°C to +150°C                |

| Power dissipation:                                        |                                |

| 16-Lead SOIC                                              | 900mW                          |

| 16-Lead PDIP                                              | 1000mW                         |

| 20-Lead PLCC                                              | 1400mW                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. **Voltages are referenced to -V**<sub>IN</sub>-

### **Typical Thermal Resistance**

| Package      | $oldsymbol{	heta}_{ja}$ |

|--------------|-------------------------|

| 16-Lead SOIC | 83°C/W                  |

| 16-Lead PDIP | 51°C/W                  |

| 20-Lead PLCC | 66°C/W                  |

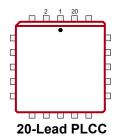

### **Pin Configurations**

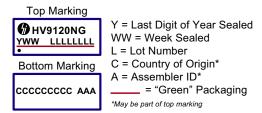

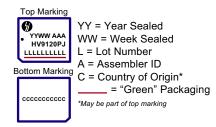

### **Product Marking**

Package may or may not include the following marks: Si or \$\mathbb{n}\$

#### 16-Lead SOIC

Package may or may not include the following marks: Si or

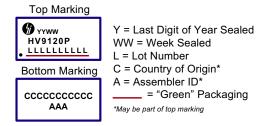

#### 16-Lead PDIP

Package may or may not include the following marks: Si or

20-Lead PLCC

<sup>\*</sup> Obsolescence notice issued for the product in the 20-Lead PLCC package.

### **Electrical Characteristics**

(Unless otherwise specified,  $V_{DD}$  = 10V, + $V_{IN}$  = 48V,  $R_{BIAS}$  = 390k $\Omega$ ,  $R_{OSC}$  = 330k $\Omega$ ,  $T_A$  = 25°C.)

| Sym                  | Parameter                                   | # | Min    | Тур      | Max  | Units  | Conditions                                                     |

|----------------------|---------------------------------------------|---|--------|----------|------|--------|----------------------------------------------------------------|

| Refere               | nce                                         |   |        | •        |      | •      | •                                                              |

|                      | Outrot valle va                             |   | 3.92   | 4.00     | 4.08 | V      | $R_L = 10M\Omega$                                              |

| $V_{REF}$            | Output voltage                              | - | 3.84   | 4.00     | 4.16 | ] V    | $R_L = 10M\Omega, T_A = -55^{\circ}C \text{ to } 125^{\circ}C$ |

| Z <sub>out</sub>     | Output impedance                            | # | 15     | 30       | 45   | kΩ     |                                                                |

| I <sub>SHORT</sub>   | Short circuit current                       | - | -      | 125      | 250  | μA     | V <sub>REF</sub> = -V <sub>IN</sub>                            |

| $\Delta V_{REF}$     | Change in V <sub>REF</sub> with temperature | # | -      | 0.25     | -    | mV/°C  | T <sub>A</sub> = -55°C to 125°C                                |

| Oscilla              | tor                                         |   |        |          |      |        |                                                                |

| f <sub>MAX</sub>     | Oscillator frequency                        | - | 1.0    | 3.0      | -    | MHz    | $R_{OSC} = 0\Omega$                                            |

| £                    | Initial acquire out                         | - | 80     | 100      | 120  | I/LI=  | $R_{OSC} = 330k\Omega$                                         |

| f <sub>osc</sub>     | Initial accuracy <sup>1</sup>               | - | 160    | 200      | 240  | kHz    | $R_{OSC} = 150k\Omega$                                         |

| $\Delta V_{\rm osc}$ | Voltage stability                           | - | -      | -        | 15   | %      | 9.5V < V <sub>DD</sub> < 13.5V                                 |

| TC <sub>osc</sub>    | Temperature coefficient                     | # | -      | 170      | -    | ppm/°C | T <sub>A</sub> = -55°C to 125°C                                |

| PWM                  |                                             |   |        |          |      |        |                                                                |

| D <sub>MAX</sub>     | Maximum duty cycle                          | # | 49.0   | 49.4     | 49.6 | %      |                                                                |

|                      | Minimum duty cycle                          | - | -      | -        | 0    | %      |                                                                |

| $D_{MIN}$            | Maximum pulse width before pulse drops out  | # | -      | 80       | 125  | ns     |                                                                |

| Curren               | t Limit                                     |   |        | 1        | 1    |        |                                                                |

| $V_{LIM}$            | Maximum input signal                        | - | 1.0    | 1.2      | 1.4  | V      | V <sub>FB</sub> = 0V                                           |

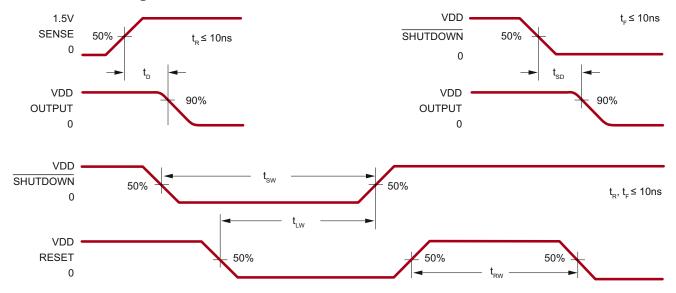

| t <sub>D</sub>       | Delay to output                             | # | -      | 80       | 120  | ns     | V <sub>SENSE</sub> = 1.5V, V <sub>COMP</sub> ≤ 2.0V            |

| Error A              | mplifier                                    | ' |        |          |      |        |                                                                |

| $V_{\sf FB}$         | Feedback voltage                            | - | 3.92   | 4.00     | 4.08 | V      | V <sub>FB</sub> shorted to COMP                                |

| I <sub>IN</sub>      | Input bias current                          | - | -      | 25       | 500  | nA     | V <sub>FB</sub> = 4.0V                                         |

| V <sub>os</sub>      | Input offset voltage                        | - | nulled | during t | rim  | -      |                                                                |

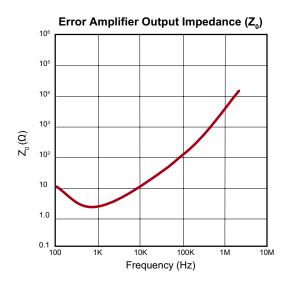

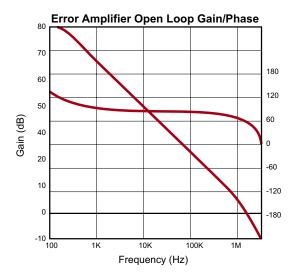

| A <sub>VOL</sub>     | Open loop voltage gain                      | # | 60     | 80       | -    | dB     |                                                                |

| GB                   | Unity gain bandwidth                        | # | 1.0    | 1.3      | -    | MHz    |                                                                |

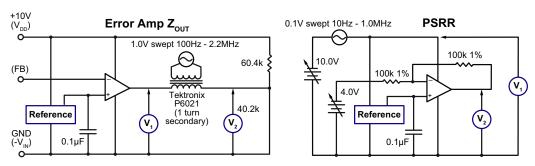

| Z <sub>out</sub>     | Out impedance                               | # | se     | e Fig. 1 |      | Ω      |                                                                |

| SOURCE               | Output source current                       | - | -1.4   | -2.0     | -    | mA     | V <sub>FB</sub> = 3.4V                                         |

| ISINK                | Output sink current                         | - | 0.12   | 0.15     | -    | mA     | V <sub>FB</sub> = 4.5V                                         |

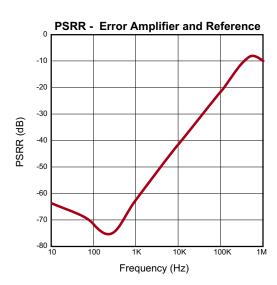

| PSRR                 | Power supply rejection                      | # | se     | e Fig. 2 | 1    | dB     |                                                                |

| Notes:               |                                             |   |        |          |      |        | I.                                                             |

#### Notes:

- # Guaranteed by design.

- 1. Stray capacitance on OSC In pin must be ≤5pF.

Electrical Characteristics (cont.) (Unless otherwise specified,  $V_{DD}$  = 10V,  $+V_{IN}$  = 48V,  $R_{BIAS}$  = 390k $\Omega$ ,  $R_{OSC}$  = 330k $\Omega$ ,  $T_A$  = 25°C.)

| Sym               | Parameter                                               |           | # | Min                   | Тур  | Max  | Units | Conditions                                                   |

|-------------------|---------------------------------------------------------|-----------|---|-----------------------|------|------|-------|--------------------------------------------------------------|

| Pre-Re            | gulator/Startup                                         |           |   |                       |      |      |       |                                                              |

| +V <sub>IN</sub>  | Input voltage                                           |           | - | 10                    | -    | 450  | V     | $I_{IN} < 10 \mu A; V_{CC} > 9.4 V$                          |

| +1                | Input leakage curren                                    | t         | - | -                     | -    | 10   | μA    | V <sub>DD</sub> > 9.4V                                       |

| $V_{TH}$          | V <sub>DD</sub> pre-regulator turn<br>threshold voltage | n-off     | - | 8.0                   | 8.7  | 9.4  | V     | I <sub>PREREG</sub> = 10μA                                   |

| V <sub>LOCK</sub> | Undervoltage lockou                                     | t         | - | 7.0                   | 8.1  | 8.9  | V     |                                                              |

| Supply            | 1                                                       |           |   |                       |      |      |       |                                                              |

| I <sub>DD</sub>   | Supply current                                          |           | - | -                     | 0.75 | 1.3  | mA    | C <sub>L</sub> < 75pF                                        |

| I <sub>Q</sub>    | Quiescent supply cu                                     | rrent     | - | -                     | 0.55 | -    | mA    | SHUTDOWN = -V <sub>IN</sub>                                  |

| I <sub>BIAS</sub> | Nominal bias current                                    |           | - | -                     | 20   | -    | μA    |                                                              |

| V <sub>DD</sub>   | Operating range                                         |           | - | 9.0                   | -    | 13.5 | V     |                                                              |

| Shutdo            | own Logic                                               |           |   |                       |      |      |       |                                                              |

| t <sub>sd</sub>   | SHUTDOWN delay                                          |           | # | -                     | 50   | 100  | ns    | $C_L = 500pF, V_{SENSE} = -V_{IN}$                           |

| t <sub>sw</sub>   | SHUTDOWN pulse width                                    |           | # | 50                    | -    | -    | ns    |                                                              |

| t <sub>RW</sub>   | RESET pulse width                                       |           | # | 50                    | -    | -    | ns    |                                                              |

| t <sub>LW</sub>   | Latching pulse width                                    |           | # | 25                    | -    | -    | ns    | SHUTDOWN and RESET low                                       |

| V <sub>IL</sub>   | Input low voltage                                       |           | - | -                     | -    | 2.0  | V     |                                                              |

| V <sub>IH</sub>   | Input high voltage                                      |           | - | 7.0                   | -    | -    | V     |                                                              |

| I <sub>IH</sub>   | Input current, input high voltage                       |           | - | -                     | 1.0  | 5.0  | μA    | $V_{IN} = V_{DD}$                                            |

| I <sub>IL</sub>   | Input current, input low voltage                        |           | - | -                     | -25  | -35  | μA    | V <sub>IN</sub> = 0V                                         |

| Output            |                                                         |           |   |                       |      |      |       |                                                              |

|                   |                                                         |           | - | V <sub>DD</sub> -0.25 | -    | -    | V     | I <sub>OUT</sub> = 10mA                                      |

| V <sub>OH</sub>   | Output high voltage                                     |           | - | V <sub>DD</sub> -0.3  | -    | -    | V     | I <sub>OUT</sub> = 10mA,<br>T <sub>A</sub> = -55°C to 125°C  |

|                   |                                                         |           | - | -                     | -    | 0.2  | V     | I <sub>OUT</sub> = -10mA                                     |

| V <sub>OL</sub>   | Output low voltage                                      |           | - | -                     | -    | 0.3  | V     | I <sub>OUT</sub> = -10mA,<br>T <sub>A</sub> = -55°C to 125°C |

|                   |                                                         | Pull up   | - | -                     | 15   | 25   | Ω     | I - 140mA                                                    |

| R <sub>out</sub>  | Output registeres                                       | Pull down | - | -                     | 8.0  | 20   | Ω     | I <sub>OUT</sub> = ±10mA                                     |

|                   | Output resistance                                       | Pull up   | - | -                     | 20   | 30   | Ω     | I <sub>OUT</sub> = ±10mA,                                    |

|                   | Pull down                                               |           | - | -                     | 10   | 30   | Ω     | T <sub>A</sub> = -55°C to 125°C                              |

| t <sub>R</sub>    | Rise time                                               |           | # | -                     | 30   | 75   | ns    | C <sub>L</sub> = 500pF                                       |

| t <sub>F</sub>    | Fall time                                               |           | # | -                     | 20   | 75   | ns    | C <sub>L</sub> = 500pF                                       |

| Note:             |                                                         |           |   |                       |      |      |       |                                                              |

# Guaranteed by design.

#### **Test Circuits**

Note:

Set feedback voltage so that  $V_{COMP} = V_{DIVIDE} \pm 1.0 \text{mV}$  before connecting transformer.

### **Detailed Description**

#### Pre regulator

The pre regulator/startup circuit for the HV9120 consists of a high-voltage n-channel depletion-mode DMOS transistor driven by an error amplifier to form a variable current path between the VIN terminal and the VDD terminal. Maximum current (about 20 mA) occurs when  $V_{\rm DD}$  = 0, with current reducing as  $V_{\rm DD}$  rises. This path shuts off altogether when  $V_{\rm DD}$  rises to somewhere between 7.8 and 9.4V, so that if  $V_{\rm DD}$  is held at 10 or 12V by an external source (generally the supply the chip is controlling), no current other than leakage is drawn through the high voltage transistor. This minimizes dissipation.

An external capacitor between VDD and VSS is generally required to store energy used by the chip in the time between shutoff of the high voltage path and the VDD supply's output rising enough to take over powering the chip. This capacitor should have a value of 100X or more the effective gate capacitance of the MOSFET being driven, i.e.,

$$C_{STORAGE} \ge 100 x$$

(gate charge of FET at 10V)

as well as very good high frequency characteristics. Stacked polyester or ceramic caps work well. Electrolytic capacitors are generally not suitable. A common resistor divider string is used to monitor  $V_{\text{DD}}$  for both the undervoltage lockout circuit and the shutoff circuit of the high voltage FET. Setting the undervoltage sense point about 0.6V lower on the string than the FET shutoff point guarantees that the undervoltage lockout always releases before the FET shuts off.

#### **Bias Circuit**

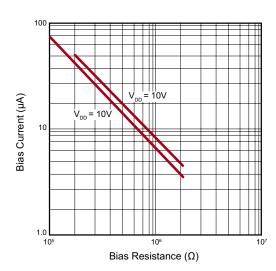

An external bias resistor, connected between the bias pin and VSS is required by the HV9120 to set currents in a series of current mirrors used by the analog sections of the chip. Nominal external bias current requirement is 15 to  $20\mu A$ , which can be set by a 390 to  $510k\Omega$  resistor if a 10V

$V_{\text{DD}}$  is used, or a 510 to  $680k\Omega$  resistor if  $V_{\text{DD}}$  will be 12V. A precision resistor is not required;  $\pm5\%$  is fine.

#### **Clock Oscillator**

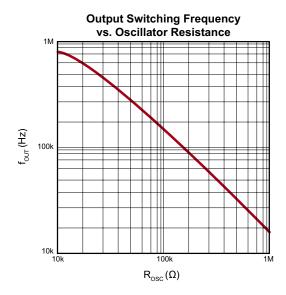

The clock oscillator of the HV9120 consists of a ring of CMOS inverters, timing capacitors, a capacitor discharge FET, and a frequency dividing flip-flop. A single external resistor between the OSC IN and OSC OUT pins is required to set oscillator frequency (see graph).

One difference exists between the Supertex HV9120 and competitive 9120s: The oscillator is shut off when a shutoff command is received. This saves about 150 $\mu$ A of quiescent current, which aids in the construction of power supplies to meet CCITT specification I-430, and in other situations where an absolute minimum of quiescent power dissipation is required.

#### Reference

The Reference of the HV9120 consists of a stable bandgap reference followed by a buffer amplifier which scales the voltage up to approximately 4.0V. The scaling resistors of the reference buffer amplifier are trimmed during manufacture so that the output of the error amplifier, when connected in a gain of -1 configuration, is as close to 4.0V as possible. This nulls out any input offset of the error amplifier. As a consequence, even though the observed reference voltage of a specific part may not be exactly 4.0V, the feedback voltage required for proper regulation will be.

A ≈ 50kΩ resistor is placed internally between the output of the reference buffer amplifier and the circuitry it feeds (reference output pin and non-inverting input to the error amplifier). This allows overriding the internal reference with a low-impedance voltage source ≤6.0V. Using an external reference reinstates the input offset voltage of the error amplifier, and its effect of the exact value of feedback voltage

required. In general, because the reference voltage of the Supertex HV9120 is not noisy, as some previous examples have been, overriding the reference should seldom be necessary.

Because the reference of the HV9120 is a high impedance node, and usually there will be significant electrical noise near it, a bypass capacitor between the reference pin and VSS is strongly recommended. The reference buffer amplifier is intentionally compensated to be stable with a capacitive load of 0.01 to  $0.1\mu F$ .

#### **Error Amplifier**

The error amplifier in the HV9120 is a true low-power differential input operational amplifier intended for around-the-amplifier compensation. It is of mixed CMOS-bipolar construction: A PMOS input stage is used so the common-mode range includes ground and the input impedance is very high. This is followed by bipolar gain stages which provide high gain without the electrical noise of all-MOS amplifiers. The amplifier is unity-gain stable.

### **Current Sense Comparators**

The HV9120 uses a true dual-comparator system with independent comparators for modulation and current limiting. This allows the designer greater latitude in compensation design, as there are no clamps (except ESD protection) on the compensation pin. Like the error amplifier, the comparators are of low-noise BiCMOS construction.

#### Remote Shutdown

The SHUTDOWN and RESET pins of the HV9120 can be used to perform either latching or non-latching shutdown of a converter as required. These pins have internal current source pull-ups so they can be driven from open-drain logic. When not used, they should be left open or connected to VDD.

#### **Output Buffer**

The output buffer of the HV9120 is of standard CMOS construction (P-channel pull-up, N-channel pull-down). Thus the body-drain diodes of the output stage can be used for spike clipping if necessary, and external Schottky diode clamping of the output is not required.

#### **Truth Table**

| SHUTDOWN          | RESET             | Output                      |

|-------------------|-------------------|-----------------------------|

| Н                 | Н                 | Normal operation            |

| Н                 | $H \rightarrow L$ | Normal operation, no change |

| L                 | Н                 | Off, not latched            |

| L                 | L                 | Off, latched                |

| $L \rightarrow H$ | L                 | Off, latched, no change     |

### **Shutdown Timing Waveforms**

### **Typical Performance Curves**

Pin Description 16-Lead SOIC

| Pin # | Description |

|-------|-------------|

| 1     | +VIN        |

| 2     | -           |

| 3     | -           |

| 4     | SENSE       |

| 5     | OUTPUT      |

| 6     | -VIN        |

| 7     | VDD         |

| 8     | OSC OUT     |

| Pin# | Description |

|------|-------------|

| 9    | OSC IN      |

| 10   | NC          |

| 11   | VREF        |

| 12   | SHUTDOWN    |

| 13   | RESET       |

| 14   | COMP        |

| 15   | FB          |

| 16   | BIAS        |

Pin Description 16-Lead PDIP

| Fill Description 16-Lead PDIP |             |  |  |  |

|-------------------------------|-------------|--|--|--|

| Pin#                          | Description |  |  |  |

| 1                             | +VIN        |  |  |  |

| 2                             | NC          |  |  |  |

| 3                             | NC          |  |  |  |

| 4                             | SENSE       |  |  |  |

| 5                             | OUTPUT      |  |  |  |

| 6                             | -VIN        |  |  |  |

| 7                             | VDD         |  |  |  |

| 8                             | OSC OUT     |  |  |  |

|                               |             |  |  |  |

| Pin# | Description |

|------|-------------|

| 9    | OSC IN      |

| 10   | NC          |

| 11   | VREF        |

| 12   | SHUTDOWN    |

| 13   | RESET       |

| 14   | COMP        |

| 15   | FB          |

| 16   | BIAS        |

Pin Description 20-Lead PLCC

| Pin # | Description |

|-------|-------------|

| 1     | NC          |

| 2     | NC          |

| 3     | +VIN        |

| 4     | NC          |

| 5     | SENSE       |

| 6     | OUTPUT      |

| 7     | NC          |

| 8     | -VIN        |

| 9     | VDD         |

| 10    | OSC OUT     |

| 8 9   | -VIN<br>VDD |

| Pin# | Description |

|------|-------------|

| 11   | OSC IN      |

| 12   | NC          |

| 13   | NC          |

| 14   | VREF        |

| 15   | NC          |

| 16   | SHUTDOWN    |

| 17   | RESET       |

| 18   | COMP        |

| 19   | FB          |

| 20   | BIAS        |

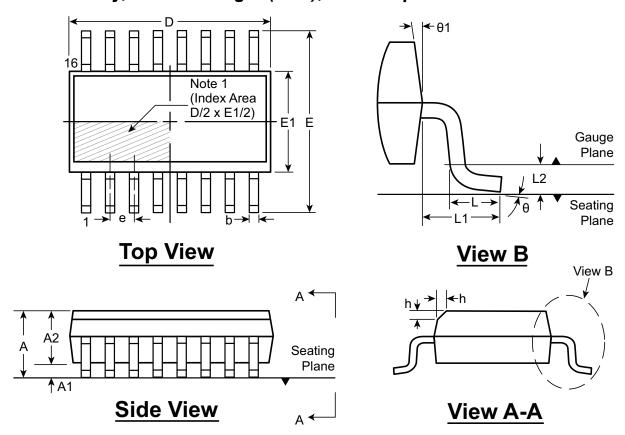

### 16-Lead SOIC (Narrow Body) Package Outline (NG)

9.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

#### Note:

1. This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbol         |     | Α     | <b>A1</b> | A2    | b    | D      | Е     | E1    | е           | h    | L    | L1          | L2          | θ          | θ1  |

|----------------|-----|-------|-----------|-------|------|--------|-------|-------|-------------|------|------|-------------|-------------|------------|-----|

|                | MIN | 1.35* | 0.10      | 1.25  | 0.31 | 9.80*  | 5.80* | 3.80* |             | 0.25 | 0.40 |             |             | <b>0</b> ° | 5°  |

| Dimension (mm) | NOM | -     | -         | -     | -    | 9.90   | 6.00  | 3.90  | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -   |

| ()             | MAX | 1.75  | 0.25      | 1.65* | 0.51 | 10.00* | 6.20* | 4.00* |             | 0.50 | 1.27 |             |             |            | 15° |

JEDEC Registration MS-012, Variation AC, Issue E, Sept. 2005.

\* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

Supertex Doc. #: DSPD-16SONG, Version G041309.

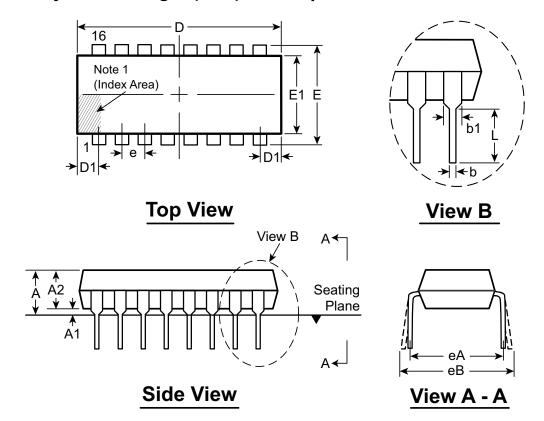

## 16-Lead PDIP (.300in Row Spacing) Package Outline (P)

.790x.250in body, .210in height (max), .100in pitch

#### Note:

A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbol             |     | Α     | A1    | A2   | b                 | b1   | D                 | D1    | E                 | E1   | е           | eА          | eВ    | L    |

|--------------------|-----|-------|-------|------|-------------------|------|-------------------|-------|-------------------|------|-------------|-------------|-------|------|

|                    | MIN | .130* | .015  | .115 | .014              | .045 | .745 <sup>†</sup> | .005  | .290 <sup>†</sup> | .240 | .100<br>BSC | .300<br>BSC | .300* | .115 |

| Dimension (inches) | NOM | -     | -     | .130 | .018              | .060 | .790              | -     | .310              | .250 |             |             | -     | .130 |

| ()                 | MAX | .210  | .035* | .195 | .023 <sup>†</sup> | .070 | .810 <sup>†</sup> | .050* | .325              | .280 |             |             | .430  | .150 |

JEDEC Registration MS-001, Variation AB, Issue D, June, 1993.

Drawings not to scale.

Supertex Doc. #: DSPD-16DIPP, Version C021312.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.

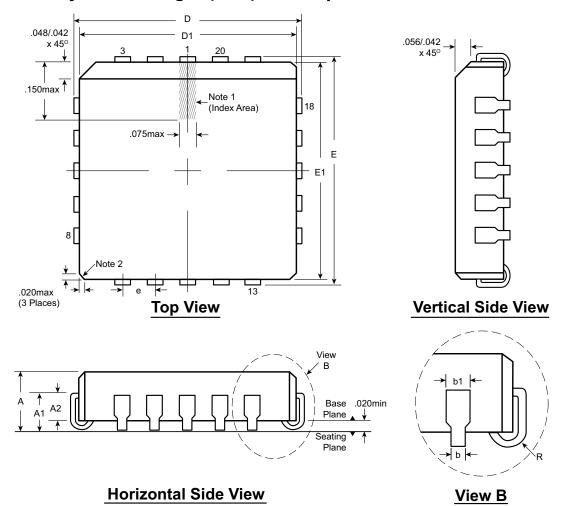

### 20-Lead PLCC Package Outline (PJ)

.353x.353in body, .180in height (max), .050in pitch

#### Notes:

- A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Actual shape of this feature may vary.

| Symbol             |     | Α    | <b>A</b> 1 | A2   | b    | b1   | D    | D1   | E    | E1   | е           | R    |

|--------------------|-----|------|------------|------|------|------|------|------|------|------|-------------|------|

|                    | MIN | .165 | .090       | .062 | .013 | .026 | .385 | .350 | .385 | .350 |             | .025 |

| Dimension (inches) | NOM | .172 | .105       | -    | -    | -    | .390 | .353 | .390 | .353 | .050<br>BSC | .035 |

| ()                 | MAX | .180 | .120       | .083 | .021 | .032 | .395 | .356 | .395 | .356 |             | .045 |

JEDEC Registration MS-018, Variation AA, Issue A, June, 1993.

Drawings not to scale.

Supertex Doc. #: DSPD-20PLCCPJ, Version C031111

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited