# Future Technology Devices International Ltd. FT4222H (USB2.0 to QuadSPI/I<sup>2</sup>C Bridge IC)

EFTDI FT4222H

FT4222H is a USB2.0 to Quad-SPI/I<sup>2</sup>C interface Device Controller with the following advanced features:

- Single chip USB2.0 Hi-speed to SPI/I<sup>2</sup>C bridge with a variety of configurations

- Entire USB protocol handled on the chip.

- On-chip OTP memory for USB Vendor ID (VID), Product ID (PID), device serial number, product description string and various other vender specific data.

- Configurable industry standard SPI Master/Slave interface controller

- Support configurable data width with single, dual, quad data width transfer mode in SPI master

- SCK can support up to 30MHz in SPI master

- Up to 28Mbps data transfer rate in SPI master with quad mode transfer

- Support single bit data transfer with full-duplex

transfer in SPI Slave

- Support up to 4 channels slave selection control pins in SPI master application

- Configurable I<sup>2</sup>C Master/Slave interface controller conforming to I<sup>2</sup>C v2.1 and v3.0 specification.

- Support 4 speed modes defined in I<sup>2</sup>C-bus Specification, standard mode (SM) up to 100Kbit/s, fast mode (FM) up to 400Kbit/s, Fast mode plus (FM+) up to 1Mbit/s, and High Speed mode (HS) up to 3.4 Mbit/s

- Configurable GPIOs can be easily controlled by software applications via USB bus

- USB Battery Charger Detection.

- Device supplied pre-programmed with unique USB serial number.

- USB Power Configurations; supports buspowered, self-powered and bus-powered with power switching.

- +5V USB VBUS detection engine

- Integrated 5V-3.3V-1.8V level converter for USB I/O.

- True 3.3V CMOS drive output and TTL input. (operates down to 1V8 with external pull-ups)

- Configurable I/O pin output drive strength; 4 mA(min) and 16 mA(max)

- Integrated power-on-reset circuit.

- USB2.0 Low operating and suspend current; 68mA (active-typ) and 375µA (suspend-typ).

- UHCI / OHCI / EHCI / XHCI host controller compatible.

- FTDI's royalty-free Direct (D2XX) drivers for Windows eliminate the requirement for USB driver development in most cases.

- Extended operating temperature range; -40 to 85°C.

- Available in compact Pb-free 32 Pin VQFN packages (RoHS compliant).

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Future Technology Devices International Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH United Kingdom. Scotland Registered Company Number: SC136640

#### **1** Typical Applications

- USB to single mode SPI master controller

- USB to dual mode SPI master controller

- USB to quad mode SPI master controller

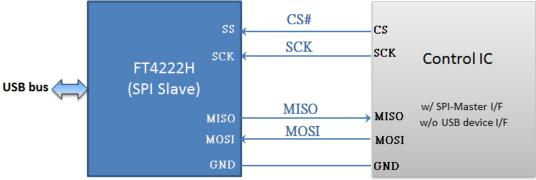

- USB to single SPI slave controller

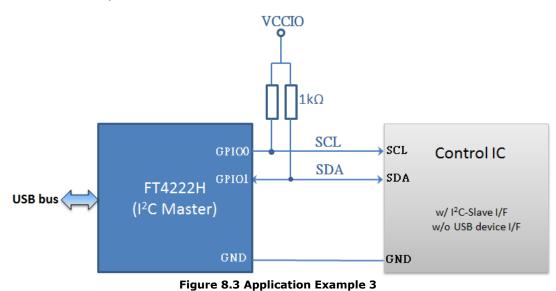

- USB to I<sup>2</sup>C master interface controller

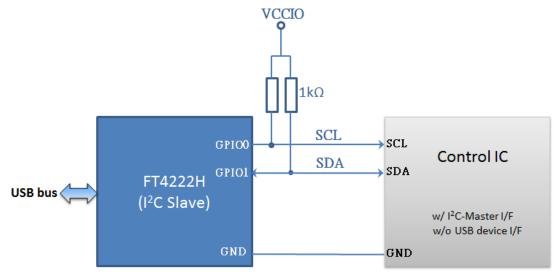

- USB to I<sup>2</sup>C slave interface controller

- Utilising USB to add system modularity

- Incorporate USB interface to enable PC transfers for development system communication

- USB Industrial Control

- USB Data Acquisition

- Accessory connectivity solutions for mobiles and tablets

- USB dongle implementations for Software/ Hardware Encryption and Wireless Modules

- Detect USB dedicated charging ports, to allow for high current battery charging in portable devices.

# 1.1 Driver Support

Royalty free D2XX Direct Drivers (USB Drivers + DLL S/W Interface)

- Windows 10 32, 64-bit

- Windows 8.1 32, 64-bit

- Windows 8 32, 64-bit

- Windows 7 32, 64-bit

- Server 2008 R2

- Server 2012 R2

For driver installation, please refer to <a href="http://www.ftdichip.com/Documents/InstallGuides.htm">http://www.ftdichip.com/Documents/InstallGuides.htm</a>

#### **1.2 Part Numbers**

| Part Number | Package     |

|-------------|-------------|

| FT4222HQ-x  | 32 Pin VQFN |

Note: Packing codes for x is:

- R: Taped and Reel, 5,000pcs per reel

- T: Tray packing, 490pcs per tray

For example: FT4222HQ-R is 5,000pcs taped and reel packing

## 1.3 USB Compliant

The FT4222H is fully compliant with the USB 2.0 specification and has been given the USB-IF Test-ID (TID) 40001599.

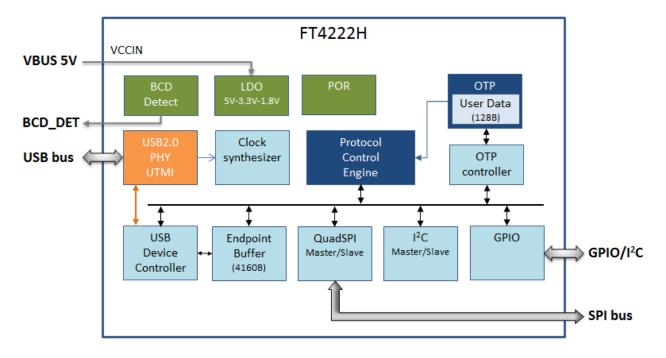

# 2 FT4222H Block Diagram

Figure 2.1 FT4222H Block Diagram

For a description of each function please refer to Section 4.

# **Table of Contents**

| 1                                                                                        | Ту                                                                          | pical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1.1                                                                                      |                                                                             | Driver Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                                                |

| 1.2                                                                                      | F                                                                           | Part Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                |

| 1.3                                                                                      | ι                                                                           | USB Compliant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                |

| 2                                                                                        | FT                                                                          | 4222H Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                |

| 3                                                                                        | De                                                                          | evice Pin Out and Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                                |

| 3.1                                                                                      |                                                                             | VQFN-32 Package Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 3.2                                                                                      | F                                                                           | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                |

| 4                                                                                        | Fu                                                                          | Inction Description1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                |

| 4.1                                                                                      |                                                                             | ·<br>Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| 4.2                                                                                      |                                                                             | ،<br>Functional Block Descriptions 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| 5                                                                                        |                                                                             | 4222H Chip Mode Configuration and SPI/I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 5.1                                                                                      |                                                                             | Chip Mode Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 5.2                                                                                      |                                                                             | SPI Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                          | <b>-</b><br>2.1                                                             | SPI Pin Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| 5.2                                                                                      | 2.2                                                                         | SPI Bus Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                               |

| 5.2                                                                                      | 2.3                                                                         | SCK Format1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                                               |

| 5.2                                                                                      | 2.4                                                                         | SPI Timing 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                               |

|                                                                                          |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 5.3                                                                                      | ]                                                                           | I <sup>2</sup> C Bus Interface 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                |

|                                                                                          | <b>]</b><br>3.1                                                             | I <sup>2</sup> C Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 5.3                                                                                      |                                                                             | I <sup>2</sup> C Pin Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>20                                                                         |

| 5.3<br>5.3<br>5.3                                                                        | 3.1<br>3.2<br>3.3                                                           | I <sup>2</sup> C Pin Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>20<br>21                                                                   |

| 5.3<br>5.3<br>5.3<br>5.3                                                                 | 3.1<br>3.2<br>3.3<br>3.4                                                    | I <sup>2</sup> C Pin Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>20<br>21<br>21                                                             |

| 5.3<br>5.3<br>5.3<br>5.3<br>5.4                                                          | 3.1<br>3.2<br>3.3<br>3.4                                                    | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2                                                                                                                                                                                                                                                                                                                                                                                            | 20<br>20<br>21<br>21<br>21                                                       |

| 5.3<br>5.3<br>5.3<br><b>5.4</b><br><b>6</b>                                              | 3.1<br>3.2<br>3.3<br>3.4<br><b>De</b>                                       | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2                                                                                                                                                                                                                                                                                                                                         | 20<br>20<br>21<br>21<br>21<br>3<br>3                                             |

| 5.3<br>5.3<br>5.3<br>5.4<br>6<br>6.1                                                     | 3.1<br>3.2<br>3.3<br>3.4<br>De                                              | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2                                                                                                                                                                                                                                                                                                | 20<br>20<br>21<br>21<br>21<br>23<br>4                                            |

| 5.3<br>5.3<br>5.3<br><b>5.4</b><br><b>6</b>                                              | 3.1<br>3.2<br>3.3<br>3.4<br>De                                              | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2                                                                                                                                                                                                                                                                                                                                         | 20<br>20<br>21<br>21<br>21<br>23<br>4                                            |

| 5.3<br>5.3<br>5.3<br>5.4<br>6<br>6.1                                                     | 3.1<br>3.2<br>3.3<br>3.4<br>De                                              | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2                                                                                                                                                                                                                                                                                                | 20<br>20<br>21<br>21<br>21<br>3<br>4<br>4<br>4                                   |

| 5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2                                                     | 3.1<br>3.2<br>3.3<br>3.4<br>(<br>De                                         | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2                                                                                                                                                                                                                                                | 20<br>20<br>21<br>21<br>21<br>3<br>4<br>4<br>4<br>4<br>5                         |

| 5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3                                              | 3.1<br>3.2<br>3.3<br>3.4<br>De                                              | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       2                                                                                                                                                                                                             | 20<br>20<br>21<br>21<br>3<br>4<br>4<br>4<br>5<br>5<br>0                          |

| 5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3<br>6.4                                       | 3.1<br>3.2<br>3.3<br>3.4<br>()<br>De                                        | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol.       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       3         OTP Memory Reliability Characteristics       3                                                                                                                                                     | 20<br>20<br>21<br>21<br>3<br>4<br>4<br>4<br>5<br>6<br>0<br>1                     |

| 5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3<br>6.4<br>7                                  | 3.1<br>3.2<br>3.3<br>3.4<br>()<br>De                                        | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol.       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       2         OTP Memory Reliability Characteristics       3         T4222H Configurations       3                                                                                                               | 20<br>20<br>21<br>21<br>3<br>4<br>4<br>4<br>5<br>6<br>0<br>1<br>5<br>1           |

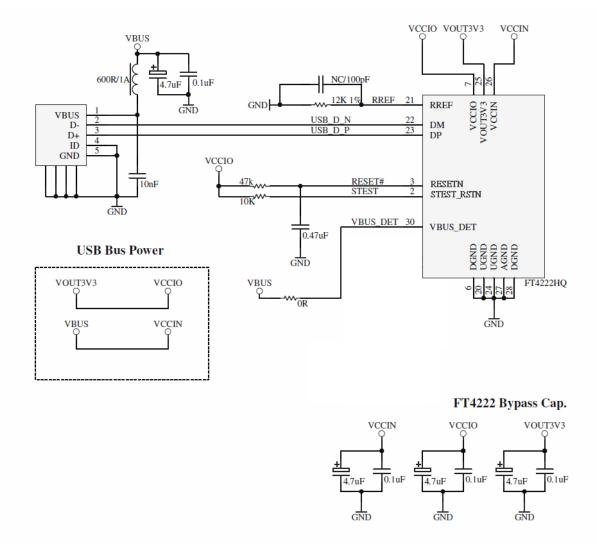

| 5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3<br>6.4<br>7<br>7.1                           | 3.1<br>3.2<br>3.3<br>3.4<br>(<br>De<br>[<br>]<br>(<br>FT                    | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol.       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       3         OTP Memory Reliability Characteristics       3         I/4222H Configurations       3         USB Bus Powered Configuration       3                                                                | 20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21 |

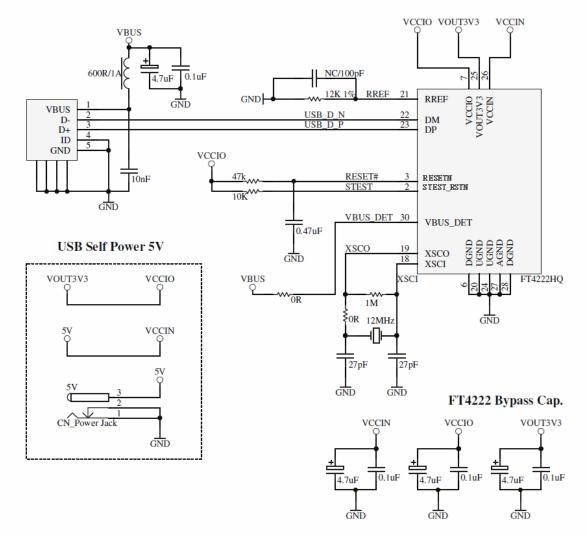

| 5.3<br>5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3<br>6.4<br>7<br>7<br>7.1<br>7.2        | 3.1<br>3.2<br>3.3<br>3.4<br>(<br>De<br>[<br>]<br>(<br>FT                    | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       2         OTP Memory Reliability Characteristics       3         IVALUATIONS       3         USB Bus Powered Configuration       3         Self Powered Configuration with 5V Source Input       3            | 20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21 |

| 5.3<br>5.3<br>5.3<br>5.4<br>6<br>6.1<br>6.2<br>6.3<br>6.4<br>7<br>7<br>7.1<br>7.2<br>7.3 | 3.1<br>3.2<br>3.3<br>3.4<br>0<br><b>De</b><br>1<br>1<br>0<br>0<br><b>FT</b> | I <sup>2</sup> C Pin Definition       2         I <sup>2</sup> C Bus Protocol.       2         I <sup>2</sup> C Slave Address       2         I <sup>2</sup> C Timing       2         GPIOs       2         evices Characteristics and Ratings       2         Absolute Maximum Ratings       2         ESD and Latch-up Specifications       2         DC Characteristics       2         OTP Memory Reliability Characteristics       3         I4222H Configurations       3         USB Bus Powered Configuration       3         Self Powered Configuration with 5V Source Input       3 |                                                                                  |

| 9 Internal OTP Memory Configuration        |    |

|--------------------------------------------|----|

| 9.1 Default Values                         | 38 |

| 9.2 Method of Programming the OTP Memory   | 41 |

| 9.2.1 Programming the OTP memory over USB  |    |

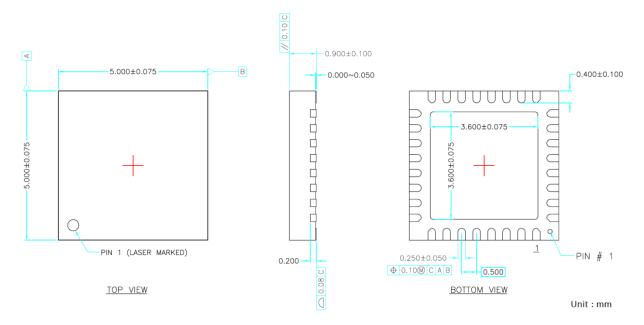

| 10 Package Parameters                      |    |

| 10.1 VQFN-32 Package Mechanical Dimensions | 42 |

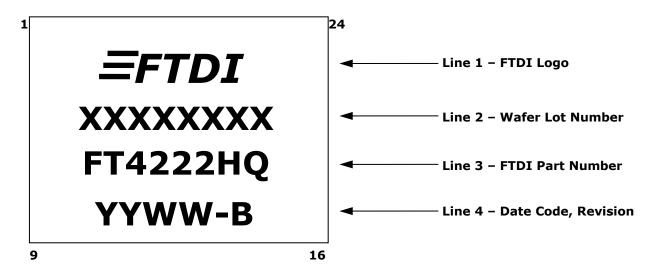

| 10.2 VQFN-32 Package Markings              | 43 |

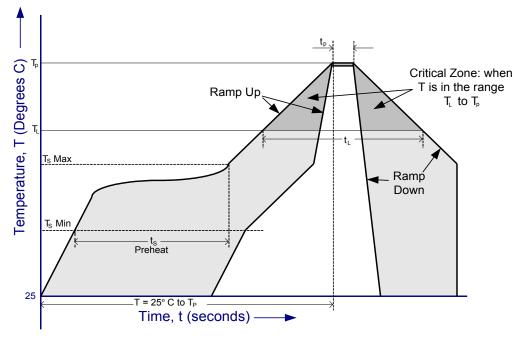

| 10.3 Solder Reflow Profile                 | 44 |

| 11 Contact Information                     | 45 |

| Appendix A – References                    | 46 |

| Appendix B - List of Figures and Tables    | 47 |

| Appendix C - Revision History              | 49 |

## 3 Device Pin Out and Signal Description

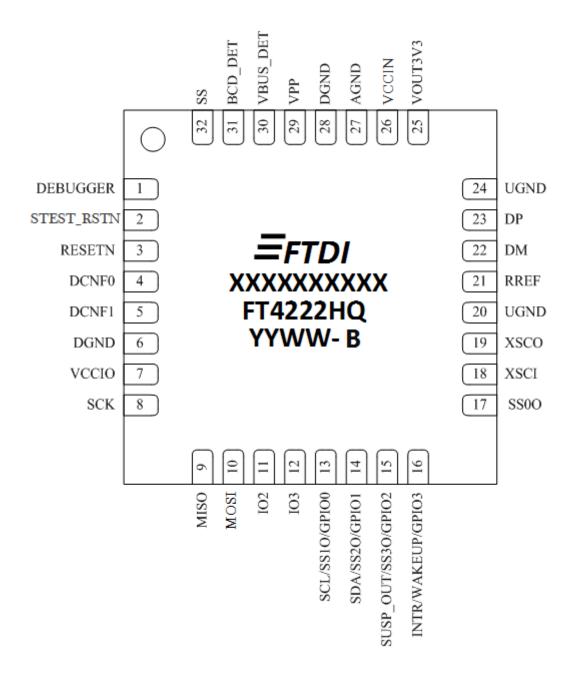

## 3.1 VQFN-32 Package Pin Out

Figure 3.1 Pin Configuration VQFN-32 (top-down view)

Document No.: FT\_001011 Clearance No.: FTDI#405

# 3.2 Pin Description

| FT4222H<br>Pin No. | Pin Name            | Туре    | Description                                                                                                                                                                 |

|--------------------|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | DEBUGGER            | I/O     | Debugging pin.<br>Should be reserved and tied to high                                                                                                                       |

| 2                  | STEST_RSTN          | Ι       | Chip reset input for test mode. Active low.<br>Should be reserved and tied to high.                                                                                         |

| 3                  | RESETN              | Ι       | Chip reset input for non-test mode operation. Active low.                                                                                                                   |

| 4                  | DCNF0               | Ι       | Chip mode configuration selection bit 0. Refer to Section 5.1                                                                                                               |

| 5                  | DCNF1               | Ι       | Chip mode configuration selection bit 1. Refer to Section 5.1                                                                                                               |

| 6                  | DGND                | Ρ       | Digital Ground                                                                                                                                                              |

| 7                  | VCCIO               | **<br>P | +3.3V/2.5V/1.8V supply voltage.<br>This is the supply voltage for all the I/O ports. This pin<br>shall be connected to pin 25 when I/O ports are working<br>at 3.3V         |

| 8                  | SCK                 | I/O     | SPI interface clock. Serial clock output for SPI master; serial clock input for SPI slave mode                                                                              |

| 9                  | MISO                | I/O     | In SPI master single mode, it is master serial data input.<br>In SPI master dual/quad mode, it is SPI data bus bit 1.<br>In SPI slave mode, it is slave serial data output. |

| 10                 | MOSI                | I/O     | In SPI master single mode, it is master serial data output.<br>In SPI master dual/quad mode, it is SPI data bus bit 0.<br>In SPI slave mode, it is slave serial data input. |

| 11                 | IO2                 | I/O     | Quad SPI data bus bit 2                                                                                                                                                     |

| 12                 | IO3                 | I/O     | Quad SPI data bus bit 3                                                                                                                                                     |

| 13                 | GPIO0/SS1O/SCL      | I/O     | GPIO 0 (default) can be configured as slave selection 1, output pin for SPI master mode or serial clock for $I^2C$ mode                                                     |

| 14                 | GPIO1/SS2O/SDA      | I/O     | GPIO 1 (default) can be configured as slave selection 2, output pin for SPI master mode or serial data for $I^2C$ mode                                                      |

| 15                 | GPIO2/SS3O/SUSP_OUT | I/O     | GPIO 2 (default) can be configured as slave selection 3,<br>output pin for SPI master mode or USB suspend output<br>indicator                                               |

| 16                 | GPIO3/WAKEUP/INTR   | I/O     | GPIO 3 (default) and can be configured as USB remote wakeup input pin or interrupt input                                                                                    |

| 17                 | SS00                | 0       | Slave selection 0, output pin for SPI master mode.                                                                                                                          |

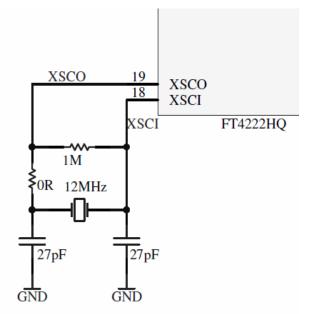

| 18                 | XSCI                | AI      | Crystal oscillator input, 12MHz only. Related application circuit can be referred to in Section7.4                                                                          |

| 19                 | XSCO                | AO      | Crystal oscillator output, 12MHz only. Related application                                                                                                                  |

1.2

Document No.: FT\_001011 Clearance No.: FTDI#405

| Pin Name | Туре                                                                        | Description                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                             | circuit can be referred to in Section7.4                                                                                                                                          |

| UGND     | Р                                                                           | USB Analog Ground                                                                                                                                                                 |

| RREF     | AI                                                                          | USB peripheral reference voltage input.<br>Connect 12Kohm +/- 1% resistor to GND.                                                                                                 |

| DM       | AI/O                                                                        | USB peripheral bidirectional DM line.                                                                                                                                             |

| DP       | AI/O                                                                        | USB peripheral bidirectional DP line.                                                                                                                                             |

| UGND     | Р                                                                           | USB Analog Ground                                                                                                                                                                 |

| VOUT3V3  | **<br>P                                                                     | +3.3V voltage Out<br>May be used to power VCCIO. When VCCIN is supplied<br>with 3.3V, this pin is a power input pin. Connect to pin 26.                                           |

| VCCIN    | **<br>P                                                                     | +5.0V(or 3.3V) supply voltage In<br>Power source-in to embedded regulator.                                                                                                        |

| AGND     | Р                                                                           | Analog Ground                                                                                                                                                                     |

| DGND     | Р                                                                           | Digital Ground                                                                                                                                                                    |

| VPP      | Р                                                                           | +6.5V supply voltage In<br>Power source for Programming embedded OTP. It should<br>be kept floating or 0V when not in programming mode                                            |

| VBUS_DET | I                                                                           | VBUS detection input. It is a +5.0V tolerant pin                                                                                                                                  |

| BCD_DET  | 0                                                                           | Battery charger detection indicator output when the device is connected to a dedicated battery charger port. Polarity can be defined                                              |

| SS       | I                                                                           | SPI slave selection indicator from SPI master. This pin is active in SPI slave mode. It must be tied to high when SPI master mode enabled.                                        |

|          | UGND RREF DM DP UGND UGND UGND VOUT3V3 VCCIN AGND DGND VPP VBUS_DET BCD_DET | UGND P<br>RREF AI<br>DM AI/O<br>DP AI/O<br>UGND P<br>UGND P<br>VOUT3V3 P<br>***<br>P<br>VCCIN **<br>P<br>AGND P<br>AGND P<br>AGND P<br>DGND P<br>VPP P<br>VBUS_DET I<br>BCD_DET O |

\*\*If VCCIN is supplied with 3.3V power input, then VOUT3V3 and VCCIO must also be driven with this 3.3V power source

## 4 Function Description

The FT4222H is a Hi-Speed USB2.0-to-Quad SPI/  $I^2C$  device controller in a compact 32-pin VQFN package. The FT4222H requires an external Crystal (12 MHz) for the internal PLL to operate. It supports multi-voltage IO, 3.3V, 2.5V or 1.8V. It also provides 128 bytes one-time-programmable (OTP) memory space for storing vendor specific information.

The FT4222H contains SPI/  $I^2C$  configurable interfaces. The SPI interface can be configured in master mode with single, dual, or quad bits data width transfer or in slave mode with single bit data width transfer. The  $I^2C$  interface can be configured in master or slave mode.

## 4.1 Key Features

**Functional Integration.** The FT4222H is a USB 2.0 Hi-Speed (480Mbits/s) to flexible and configurable SPI or I<sup>2</sup>C interfaces IC. The FT4222H includes an integrated +1.8V and +3.3V Low Drop-Out (LDO) regulator and 12MHz to 480MHz PLL. It also includes Power-On-Reset (POR), VBUS detection with 5V-tolerance and 128 bytes one-time-programmable(OTP) memory which simplify external circuit design and reduce external component count.

**USB2.0 Hi-Speed Device Controller**. The FT4222H integrates a USB protocol engine which controls the physical Universal Transceiver Macrocell Interface (UTMI) and handles all aspects of the USB 2.0 Hi-Speed interface. It contains one control endpoint, and 4-pairs of IN and OUT endpoints. These endpoints can implement up to 4 independent interfaces/applications mapped to combined I<sup>2</sup>C, GPIO, SPI interfaces.

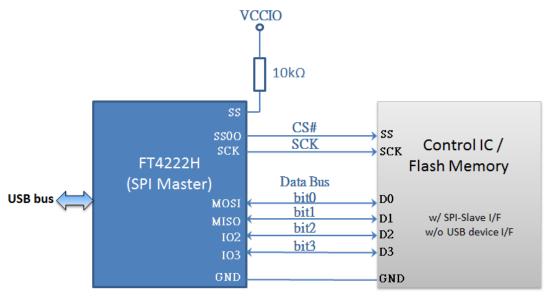

**Highly Integrated USB2.0 to Configurable SPI Bridge**. The FT4222H provides the bridge function between a USB2.0 device, upstream port and an SPI Master/Slave.

A support library, LibFT4222, based on FTDI's D2XX driver, enables easy configuration of the SPI as a master or slave. Operating clock frequency on the SPI bus, clock phase and polarity, transfer data bit width mode, and the number of slave selection controls are also configurable.

The maximum SPI interface operating clock can be set up to 40MHz in master mode and 20MHz in slave mode. With quad mode (4-bits) data bus width, the max data transfer throughput can be up to 28Mbps.

**USB to Configurable I<sup>2</sup>C Controller.** The FT4222H also provides the bridge function between a USB2.0 device upstream port and an I<sup>2</sup>C Master/Slave interface.

A support library, LibFT4222, based on FTDI's D2XX driver, enables easy configuration of the  $I^2C$  as either a master or slave, including target operating speed and bus protocol on the  $I^2C$  bus.

The device can run at common  $I^2C$  bus speeds, standard mode (SM), fast mode (FM), Fast mode plus (FM+), and High Speed mode (HS). A higher bit rate on the  $I^2C$  bus is also configurable up to 6.66Mbit/s. Clock stretching is supported to conform to v2.1 and v3.0 of the  $I^2C$  specification.

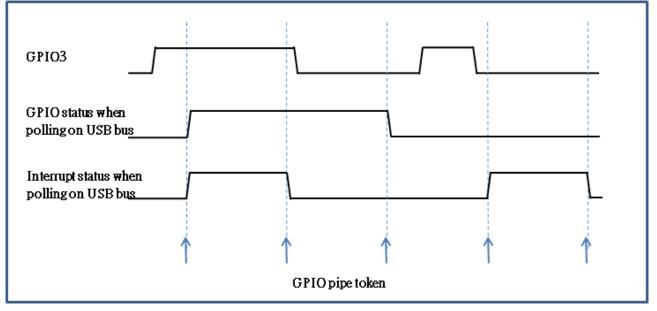

**Configurable GPIOs.** There are 4 GPIO pins in the FT4222H that can be configured for different purposes, such as a suspend indicator output, remote wake up input, an interrupt input or general purpose Input/Output. These GPIOs can be easily initialized and fully controlled at the USB host side by the application programming interface (API) defined in LibFT4222.

Signal drive strength and slew rate of these GPIOs can be configured via the FT\_Prog utility for different design needs.

**Embedded OTP memory.** The internal OTP memory in the FT4222H is used to store USB Vendor ID (VID), Product ID (PID), device serial number, product description string and various other USB configuration descriptors. With this embedded OTP memory, the device can store vendor specific information and save the cost on BOM. The descriptors can be programmed using the FTDI utility software called FT\_PROG, which can be downloaded from the FTDI Utilities page on the FTDI website (http://www.ftdichip.com/Support/Utilities.htm#FT\_Prog).

**Power management.** USB 2.0 suspend/resume and remote wakeup are fully supported. The PHY will be put to a power saving mode and the clock to most of the digital circuits will be stopped when the device is suspended.

**Source Power and Power Consumption.** The FT4222H is capable of operating at a voltage supply of +3.3V or +5.0V with a nominal operational mode current of 68mA and a nominal USB suspend mode current of 375µA. This allows greater margin for peripheral designs to meet the USB suspend mode current limit of 2.5mA. An integrated level converter within the FT4222H allows the device to interface with logic running at +1.8V, 2.5V or +3.3V. (Note: External pull-ups are recommended for IO <3V3).

## 4.2 Functional Block Descriptions

The following paragraphs detail each function within the FT4222H. Please refer to the block diagram shown in **Figure 2.1**

**USB2.0 UTMI PHY**. The Universal Transceiver Macrocell Interface (UTMI) is a physical interface cell. This block handles the full speed and high speed SERDES (serialise - deserialise) function for the USB TX/RX data. It also provides the clocks for the rest of the chip. A 12 MHz crystal should be connected to the XSCI and XSCO pins. A 12k Ohm resistor should be connected between REF and GND on the PCB.

The UTMI PHY functions include:

- Supports 480 Mbit/s "Hi-Speed" (HS) and 12 Mbit/s "Full Speed" (FS).

- SYNC/EOP generation and checking.

- Data and clock recovery from a serial stream on the USB.

- Bit-stuffing/unstuffing; bit stuff error detection.

- Manages USB Resume, Wake Up and Suspend functions.

Single parallel data clock output with on-chip PLL to generate higher speed serial data clocks

**USB Device Controller.** The USB Device controller in the FT4222H controls and manages the interface between the UTMI PHY and the interfaces of the chip. It provides 9 endpoints to fit into the FT4222H applications.

The USB Device Controller function includes:

- Endpoint-0 for a control pipe with max packet size 64 Bytes

- 4 endpoints for bulk-in pipe with configurable max packet size up to 512 Bytes

- 4 endpoints for bulk-out pipe with configurable max packet size up to 512 Bytes

- Multiple interfaces configuration support

- Suspend detection and power management

- Remote wake-up support

- Fully compatible to USB2.0 specification requirement

**Endpoint Buffer.** For fulfilling the max packet size requirement and high performance data transfer throughput, the Endpoint Buffer is 4160 bytes SRAM with configurable size management to each endpoint. It can be configured as single or double buffers and adjustable size for each endpoint.

**QuadSPI Master/Slave Controller.** The QuadSPI is a fully configurable SPI master/slave device, which allows the user to configure polarity and phase of the serial clock signal SCK. When SPI is configured as a master, it can be configured automatically to drive slave select outputs (SS3O – SS0O), and address the SPI slave device to exchange serially shifted data. The data bus can be configured as single (1bit), dual (2-bits) and quad (4-bits) mode for different transfer requests and applications. The interface operating clock can be easily configured up to 30MHz. When SPI is configured as a slave, the SPI engine can support one slave port and operate a single data mode transfer. The max acceptable operating clock can be up to 20MHz. The QuadSPI controller can be configured via a support library, LibFT4222. For details refer to the <u>User Guide For LibFT4222</u>.

QuadSPI as master functions include:

- Single Mode (1-bit) data transfer with full duplex serial data transfer

- Dual Mode (2-bit) data transfer

- Quad Mode (4-bit) data transfer

- Up to 4 SPI slave channels can be addressed via pins SS30~SS00

- Shared data bus to minimize related pin counts

- 4 types of transfer format can be selected by Phase and Polarity

- Configurable interface clock on SCK as 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256 of 80MHz, 60MHz,48MHz and 24MHz

1.2

Document No.: FT\_001011 Clearance No.: FTDI#405

| SCK F              | Freq. (Hz)                        | SCK = Operating Clock $*$ the following ratio |      |      |       |        |        |         |          |

|--------------------|-----------------------------------|-----------------------------------------------|------|------|-------|--------|--------|---------|----------|

| Operating<br>Clock | Max Throughput<br>can be expected | 1/2                                           | 1/4  | 1/8  | 1/16  | 1/32   | 1/64   | 1/128   | 1/256    |

| 80MHz              | 28.1Mbps*                         | 40M*                                          | 20M* | 10M  | 5M    | 2.5M   | 1.25M  | 625K    | 312.5K   |

| 60MHz              | 20.5Mbps*                         | 30M*                                          | 15M  | 7.5M | 3.75M | 1.875M | 937.5K | 468.75K | 234.375K |

| 48MHz              | 16.3Mbps*                         | 24M*                                          | 12M  | 6M   | 3M    | 1.5M   | 750K   | 375K    | 187.5K   |

| 24MHz              | 8.0Mbps*                          | 12M*                                          | 6M   | 3M   | 1.5M  | 750K   | 375K   | 187.5K  | 93.75K   |

Table 4.1 SCK Operating Frequency in SPI Master Mode

\*The max. throughput can be expected under the condition of quad mode transfers with a high operating frequency on SCK. It also depends on the USB bus transfer condition. For example, the max throughput that can be expected is up to 28.1Mbps when the operating clock is equal to 80MHz, SCK is set as 20MHz or 40MHz, the data bus is operating in quad mode and the USB bus is operating at hi-speed USB rates with sufficient bandwidth.

QuadSPI as slave functions include:

- Single Mode (1-bit) data transfer with full duplex serial data transfer

- Can accept SCK operating frequency up to 20 MHz

| Operating Clock Frequency | Max Acceptable Frequency on SCK |

|---------------------------|---------------------------------|

| 80MHz                     | <= 20MHz                        |

| 60MHz                     | <= 15MHz                        |

| 48MHz                     | <= 12MHz                        |

| 24MHz                     | <= 6MHz                         |

Table 4.2 Max. Acceptable Operating Frequency on SCK in SPI Slave Mode

**I<sup>2</sup>C Master/Slave Controller.** I<sup>2</sup>C (Inter Integrated Circuit) is a multi-master serial bus invented by Philips. I<sup>2</sup>C uses two bi-directional open-drain wires called serial data (SDA) and serial clock (SCL). Common I<sup>2</sup>C bus speeds are the standard mode (SM) with bit rate up to 100 Kbit/s, fast mode (FM) with the bit rate up to 400 kbit/s, Fast mode plus (FM+) with the bit rate up to 1 Mbit/s, and High Speed mode (HS) with the bit rate up to 3.4 Mbit/s. Refer to the I<sup>2</sup>C specification for more information on the protocol.

The FT4222H device can operates as master or slave, and the major functions include:

- Master or slave mode configurable

- Fully compatible to v2.1 and v3 specification

- 7-bit address support

- Support 4 speed configurations defined in I<sup>2</sup>C-bus specification

- Support bit rate up to 6.66Mbit/s both in master and slave mode

- Clock stretching support in master and slave mode

**GPIOs.** FT4222H contains 4 GPIO pins for various functions. The drive strength, slew rate control and pull high/low resistors can be configured in the vendor configurable area of the OTP via FT\_PROG. When the USB GPIO interface is enabled and supported, GPIOs can be directly controlled by APIs (Application Programming Interface) which are defined in the support library, LibFT4222, to match the requirement.

GPIOs in the FT4222H functions include:

- GPIO0 can be configured as GPIO0 or I<sup>2</sup>C SCL or SPIM slave selection SS10

- GPIO1 can be configured as GPIO1 or I<sup>2</sup>C SDA or SPIM slave selection SS20

Chip

- GPIO2 can be configured as GPIO2 or USB suspend status output(SUSP) or SPIM slave selection SS30

- GPIO3 can be configured as GPIO3 or USB remote wake-up input(WAKE) or external interrupt input(INTR)

- Adjustable Driving Strength : 4mA/8mA/12mA/16mA

- Slew Rate, Pull High/Low resistor, open drain configurable

- WAKE can be configured as rising or falling edge triggered

- SUSP trigger mode can be configured as rising edge, falling edge, high level and low level trigger

For configuration details refer to Section 9.1.

**Built-in Clock Synthesizer.** With an on-chip clock synthesizer, the FT4222H may operate with a lowcost 12 MHz crystal (or oscillator) by connecting to XSCI and XSCO, and generates a standard internal 480 MHz clock for the USB interface. The Clock Synthesizer takes the 480MHz clock from the embedded UTMI PHY and generates the 80MHz, 60MHz, 48MHz and 24MHz as reference clocks. The user can select one of these reference clocks via the API, FT4222\_SetClock which is defined in LibFT4222, as the system operating clock. The system operating clock will be the base and used by the embedded functions to generate the required interface clock.

**Protocol Control Engine.** The FT4222H has an embedded and robust control engine. It deals with the USB enumeration commands and flow control between driver and function such as SPI or I<sup>2</sup>C devices. It can perform the bridge function initialization and enable an exceptional data transfer performance through the USB bus. It collects and summarizes the SPI and I<sup>2</sup>C bus protocol and simplifies the protocol as a command set via the USB Bulk transfer pipe. A support library, LibFT4222, is defined for the FT4222H and is responsible for communicating with this protocol engine. With related APIs (Application Programming Interface) defined in LibFT4222, this control engine provides a very flexible USB bridge for SPI and I<sup>2</sup>C bus access suitable for a wide range of applications.

**OTP Controller + Internal OTP Memory.** The internal OTP memory provides storage for vendor configuration data. This vendor configuration area, named as user area, is used to store USB Vendor ID (VID), Product ID (PID), device serial number, product description string and various other USB configuration descriptors. It is also used to configure the function pins capability. For further details refer to Section 9. This user area in the internal OTP memory is available to system designers to allow storing additional data from the user application over USB. The internal OTP memory can be programmed in circuit, over USB with an external voltage requirement on VPP pin (6.5V). The descriptors can be programmed using the FTDI utility software called FT\_PROG, which can be downloaded from FTDI Utilities on the FTDI website (http://www.ftdichip.com/Support/Utilities.htm#FT\_Prog).

**5V-3.3V-1.8V LDO regulator.** The LDO will regulate out 2 reference voltages for use within the FT4222H. The +3.3V LDO regulator generates the +3.3V reference voltage for driving the USB transceiver cell output buffers. It requires an external decoupling capacitor to be attached to the VOUT3V3 regulator output pin. Another +1.8V LDO regulator generates the +1.8V reference voltage for driving the internal core of the IC.

**POR RESET Generator.** POR is the integrated Power on Reset Generator Cell providing a reliable poweron reset to the device internal circuitry at power up. There is also a RESETN input pin allowing an external device to reset the FT4222H. RESETN can be tied to VCCIO (+3.3v) if not being used.

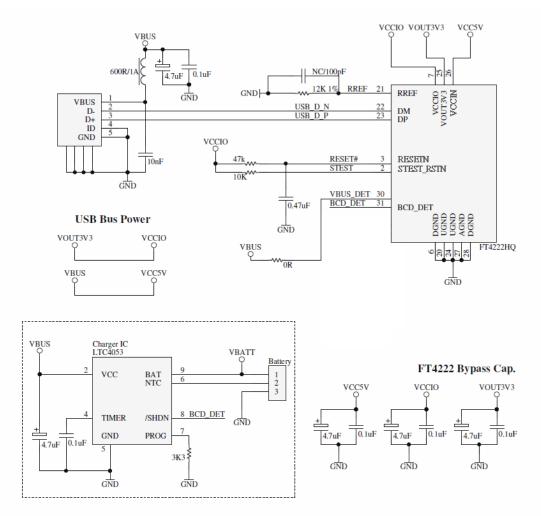

**Embedded BCD Detection.** Supports Battery Charger Detection. The BCD\_DET pin will be active if the device is connected to a dedicated charger instead of a standard USB Host. Refer to section 7.5 for an example application circuit.

## 5 FT4222H Chip Mode Configuration and SPI/I<sup>2</sup>C Interface

## 5.1 Chip Mode Configuration

The FT4222H has 4 configuration modes selected by {DCNF1, DCNF0}. The chip configuration mode will determine the number of USB interfaces for data streams and for GPIO control. The data stream interface is for data transfer between the USB2.0 host and the SPI/  $I^2C$  device. The purpose of the GPIO interface is for fully controlling the GPIOs. The following table shows the pin functions corresponding to the chip configuration mode.

| Pin Functions                                                    | CNFMODE0<br>{DCNF1, DCNF0} = 00  | CNFMODE1<br>{DCNF1, DCNF0} = 01  | CNFMOD2<br>{DCNF1, DCNF0} = 10 | CNFMODE3<br>{DCNF1, DCNF0} = 11 |

|------------------------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|---------------------------------|

| USB interface number                                             | 1 for data stream<br>1 for GPIOs | 3 for data stream<br>1 for GPIOs | 4 for data stream              | 1 for data stream               |

| SPI Master(SPIM) related pins<br>(SCK, MISO, MOSI, IO2,IO3,SSOO) | SPIM*                            | Active<br>USB interface-0        | Active<br>USB interface-0      | SPIM*                           |

| SPI Slave(SPIS) related pins<br>(SCK, MISO, MOSI, SS)            | SPIS*                            | Disable                          | Disable                        | SPIS*                           |

| GPIO0                                                            | GPIO/SCL*                        | SS10<br>USB interface-1          | SS10<br>USB interface-1        | SCL*                            |

| GPIO1                                                            | GPIO/SDA*                        | SS2O<br>USB interface-2          | SS2O<br>USB interface-2        | SDA*                            |

| GPIO2                                                            | GPIO/SUSP                        | GPIO/SUSP                        | SS3O<br>USB interface-3        | SUSP                            |

| GPIO3                                                            | GPIO/WAKE/INTR                   | GPIO/WAKE/INTR                   | WAKE                           | WAKE                            |

#### Table 5.1 FT4222H Pin Functions on Chip Configuration Mode

\*One of the SPIM, SPIS, I<sup>2</sup>C function is selected, the other 2 functions will be disabled

Note that GPIOx pins cannot be controlled by the software driver when GPIOx pins play the role as SPIM SSxO,  $I^2C$  SCL/SDA, SUSP or WAKE.

Chip Configuration only determines the number of interface/functions supported but do not decide which bus interface (SPI/  $I^2C$  /GPIO) or which role (master/slave) that the FT4222H will take. The user can use the initialisation APIs provided by the support library, LibFT4222, to configure which interface and role will be taken.

The support library for FT4222H, LibFT4222, which is based on D2XX, provides high-level and convenient APIs (Application Programming Interface) to speed up user application development. For further details refer to the <u>User Guide For LibFT4222</u>.

## 5.2 SPI Bus Interface

#### 5.2.1 SPI Pin Definition

The QuadSPI function in the FT4222H is a fully configurable SPI master/slave device. Users can utilize the API in LibFT4222, FT4222\_SPIMaster\_Init or FT4222\_SPISlave\_Init, to select in which mode (master or slave) the FT4222H will function. When the FT4222H is set as a USB-to-SPI bridge function, and chip configuration mode is chosen, the pins of the FT4222H will be mapped accordingly. The SPI related pins are

- Clock SCK (pin-8), 4 types of transfer formats supported, details refer to Section5.2.2

- Data MISO (pin-9), data transfer from slave to master for single mode, or

data bus bit-1 for dual and quad mode

- MOSI (pin-10), data transfer from master to slave for single mode, or

data bus bit-0 for dual and quad mode

- IO2 (pin-11), data bus bit-2 for quad mode

- IO3 (pin-12), data bus bit-3 for quad mode

- Slave Selection when QuadSPI acts as SPI master

- SS00 (pin-17), slave selection to slave device-0

- SS10 (pin-13), slave selection to slave device-1

- SS20 (pin-14), slave selection to slave device-2

- SS30 (pin-15), slave selection to slave device-3

- Slave Selection when QuadSPI acts as SPI slave

- SS (pin-32), slave selection for SPI master control. Must tie high when QuadSPI acts as SPI master

#### **5.2.2 SPI Bus Protocol**

The QuadSPI allows SPI data transfers in three types of bit width:

- Single SPI transfer Standard data transfer format data is read and written simultaneously

- DUAL SPI Transfer/Receive Data is transferred out or received in on 2 SPI lines simultaneously

- QUAD SPI Transfer/Receive Data is transferred out or received in on 4 SPI lines simultaneously

The operating bit width in single, dual or quad mode can also be determined by these 2 APIs, FT4222\_SPIMaster\_Init and FT4222\_SPISlave\_Init, which are defined in LibFT4222 when the SPI function is enabled and selected.

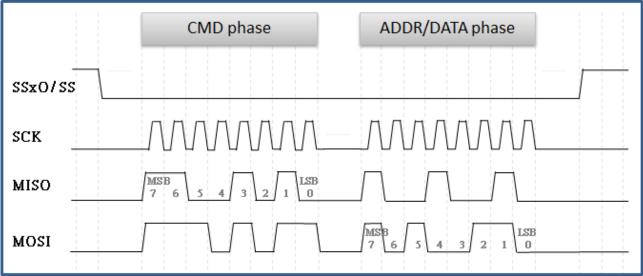

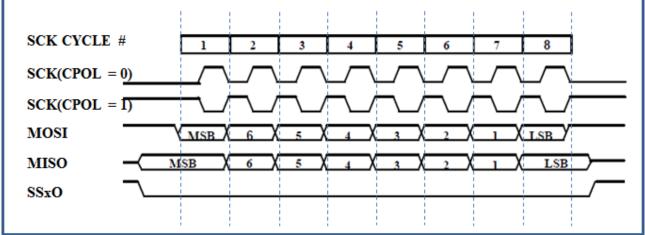

When the FT4222H is operating as an SPI master or slave device, QuadSPI can transfer data in single bit mode with full-duplex transmission. Figure 5.1 shows the basic protocol in single transfer mode

Figure 5.1 QuadSPI Bus Protocol when Transferring in Single Mode

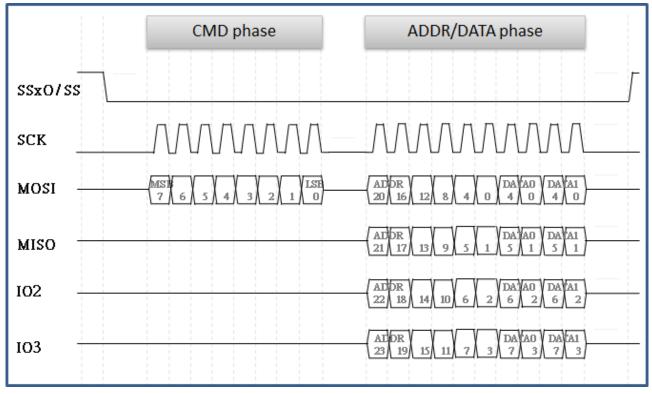

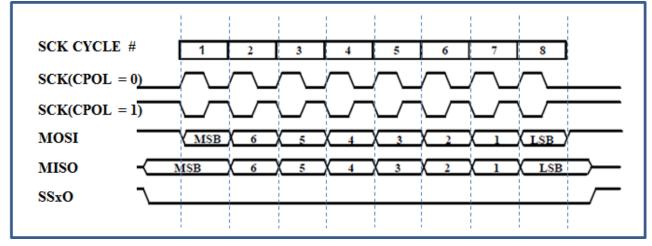

QuadSPI can operate in dual or quad transfer mode when QuadSPI is programmed as an SPI master. These multi-bit transfer modes can speed up the data transfer rate between QuadSPI and the SPI slave device supporting the multi-bit transfer. Figure 5.2 shows the bus protocol in dual or quad mode

Figure 5.2 QuadSPI Bus Protocol when Transferring in Quad Mode

#### 5.2.3 SCK Format

Software can select any of four combinations of serial clock (SCK) phase and polarity. The clock polarity is specified by the CPOL control bit, which selects an active high or active low clock and has no significant effect on the transfer format. The clock phase (CPHA) control bit selects one of two fundamentally different transfer formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transfers to allow a master device to communicate with peripheral slaves having different requirements. The flexibility of the SPI system on the QuadSPI allows direct interface to almost any existing synchronous serial peripheral. Users can also use the FT4222\_SPIMaster\_Init API which is defined in the support library LibFT4222 to select the operating phase and polarity of SCK.

#### 5.2.3.1 CPHA=0 Transfer Format

Figure 5.3 shows a timing diagram of an SPI transfer where CPHA is equal to 0. Two waveforms are shown for SCK: one for CPOL equal to 0 and another for CPOL equal to 1. The diagram may be interpreted as a master or slave timing diagram since the SCK, master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master.

Figure 5.3 SCK Transfer Format when CPHA=0

#### 5.2.3.2 CPHA=1 Transfer Format

Figure 5.4 is a timing diagram of an SPI transfer where CPHA equal to 1. Two waveforms are shown for SCK: one for CPOL equal to 0 and another for CPOL equal to 1. The diagram may be interpreted as a master or slave timing diagram since the SCK, MISO, and MOSI pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The SS line is the slave select input to the slave.

Figure 5.4 SCK Transfer Format when CPHA=1

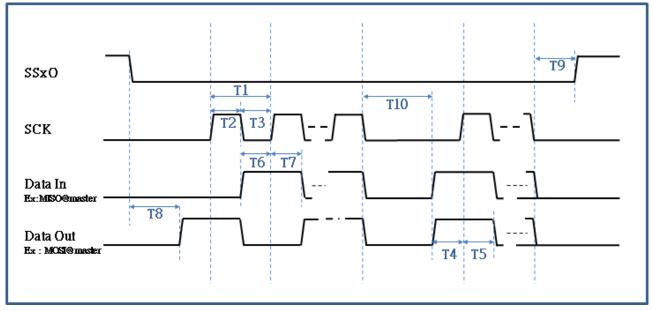

5.2.4 SPI Timing

Figure 5.5 SPI Timing

The Table5.2 shows the timing information for QuadSPI. The result is under the condition of all the related pins with 5pF loading. T6 is the required setup time to the related SCK edge for the input data path of QuadSPI. The minimum value of T4 means that the guaranteed setup time to the related SCK edge for connected device to fetch data from QuadSPI. The maximum value of T6 means that data can be accepted correctly by QuadSPI with 5pF pin loading assumed. If the pin load is larger, the timing should be considered conservatively.

| Parameter  | Min (ns) | Typ(ns) | Max(ns)     | Description                                                    |

|------------|----------|---------|-------------|----------------------------------------------------------------|

| T1@master  | T2+T3    |         |             | SCK Period when QuadSPI as master                              |

| T1@slave   | 50       |         |             | Acceptable SCK Period when QuadSPI as slave device             |

| Т2         | 12.5     |         |             | SCK HIGH, related to the operating clock and ratio             |

| Т3         | 12.5     |         |             | SCLK LOW, related to the operating clock and ratio             |

| T4         | T3-2.0   |         | T3-1.1      | Data output path: setup time to corresponding SCK edge         |

| Т5         | T2+0.1   |         | T2+0.6      | Data output path: hold time to corresponding SCK edge          |

| Т6         | 4.9      |         | 9.8         | Data input path: required setup time to corresponding SCK edge |

| Т7         |          |         | 0.1         | Data input path: required hold time to corresponding SCK edge  |

| Т8         |          | 6*T1    |             | SSxO setup time to 1 <sup>st</sup> SCK period boundary         |

| Т9         |          | 6*T1    |             | SSxO hold time from last SCK period boundary                   |

| T10@master |          | 6*T1    |             | Idle time on SCK between byte boundary when master             |

| T10@slave  | 0        |         | Timin a fam | Idle time on SCK between byte boundary when slave              |

Table 5.2 SPI Timing for VCCIO=3.3V with 5pF output pin load

Table5.3 shows the timing information for QuadSPI with VCCIO equal to 1.8V and with 5pF loading on all the related pins. The required setup time for input path is increasing since VCCIO=1.8V. The maximum operating frequency of SCK is recommended not exceeded 30MHz.

| Parameter  | Min (ns) | Typ(ns) | Max(ns) | Description                                                    |

|------------|----------|---------|---------|----------------------------------------------------------------|

| T1@master  | T2+T3    |         |         | SCK Period when QuadSPI as master                              |

| T1@slave   | 50       |         |         | Acceptable SCK Period when QuadSPI as slave device             |

| Т2         | 16.67    |         |         | SCK HIGH, related to the operating clock and ratio             |

| Т3         | 16.67    |         |         | SCLK LOW, related to the operating clock and ratio             |

| T4         | T3-2.1   |         | T3-1.2  | Data output path: setup time to corresponding SCK edge         |

| Т5         | T2+0.1   |         | T2+0.6  | Data output path: hold time to corresponding SCK edge          |

| Т6         | 8.6      |         | 16.5    | Data input path: required setup time to corresponding SCK edge |

| Т7         |          |         | 0.1     | Data input path: required hold time to corresponding SCK edge  |

| Т8         |          | 6*T1    |         | SSxO setup time to 1 <sup>st</sup> SCK period boundary         |

| Т9         |          | 6*T1    |         | SSxO hold time from last SCK period boundary                   |

| T10@master |          | 6*T1    |         | Idle time on SCK between byte boundary when master             |

| T10@slave  | 0        |         |         | Idle time on SCK between byte boundary when slave              |

Table 5.3 SPI Timing for VCCIO=1.8V with 5pF output pin load

# 5.3 I<sup>2</sup>C Bus Interface

$I^2C$  (Inter Integrated Circuit) is a multi-master serial bus invented by Philips.  $I^2C$  uses two bi-directional open-drain wires called serial data (SDA) and serial clock (SCL). Common  $I^2C$  bus speeds are standard mode (SM) with bit rate up to 100 Kbit/s, fast mode (FM) with bit rate up to 400 Kbit/s, Fast mode plus (FM+) with bit rate up to 1 Mbit/s, and High Speed mode (HS) with the bit rate up to 3.4 Mbit/s.

An I<sup>2</sup>C bus node can operate either as a master or a slave:

- Master node issues the clock and addresses slaves

- Slave node receives the clock line and address.

The FT4222H can operate as a master or slave, and is capable of being set to the speed modes defined in the  $I^2C$  bus specification. Besides the speed mode defined in the  $I^2C$  standard specification, the  $I^2C$  controller of the FT4222H can support flexible SCL frequencies defined by the following function

SCL Freq =

$$\frac{\text{Operating Clock Frequency}}{M*(N+1)}$$

$M = 6 \text{ or } 8; N = 1, 2, 3, \dots, 127$

When the target frequency is below 100 KHz, M will be equal to 8; otherwise, M will be equal to 6. For example, to generate a 2.5MHz frequency on SCL, M will be selected as 6. Then with an operating clock frequency equal to 60MHz the user can set N as 3. The SCL frequency for I<sup>2</sup>C master mode can be set via the FT4222\_I2CMaster\_Init command defined in the support library, LibFT4222. Refer to the <u>User Guide</u> For LibFT4222 for further details.

#### 5.3.1 I<sup>2</sup>C Pin Definition

The I<sup>2</sup>C function in the FT4222H is a fully configurable I<sup>2</sup>C master/slave device. When the chip configuration is set as CNFMODE0 or CNFMODE3 and the USB-to-I<sup>2</sup>C bridge function is enabled via the FT4222\_I2CMaster\_Init API which is defined in the support library LibFT4222. The pins of the FT4222H will be mapped accordingly. The I<sup>2</sup>C pins are

• Clock – SCL (pin-13), as clock output with open-drain design when I<sup>2</sup>C bus is set as master.

as clock input when I<sup>2</sup>C bus is set as slave.

• Data – SDA (pin-14), command/address/data transfer between master and slave with open-

drain design

#### **5.3.2 I<sup>2</sup>C Bus Protocol**

There are four potential modes of operation for a given bus device, although most devices only use a single role (Master or Slave) and its two modes (Transmit and Receive):

- Master transmit sending data to a slave

- Master receive receiving data from a slave

- Slave transmit sending data to a master

- Slave receive receiving data from the master

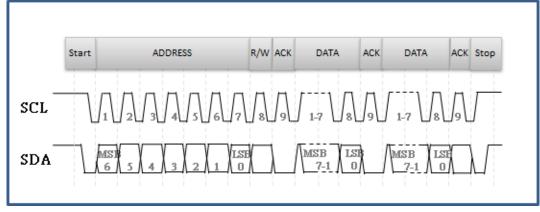

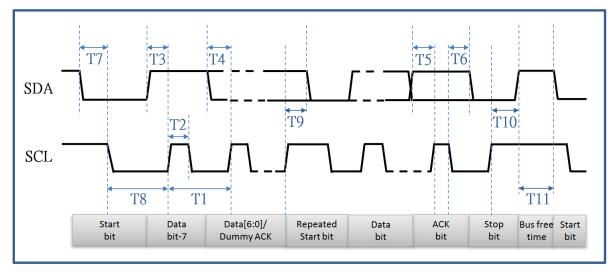

The following figure shows the basic I<sup>2</sup>C bus protocol

Figure 5.6 I<sup>2</sup>C Bus Protocol

The master is initially in master transmit mode by sending a start bit followed by the 7-bit address of the slave it wishes to communicate with, which is finally followed by a single bit representing whether it wishes to write(0) to or read(1) from the slave.

If the slave exists on the bus then it will respond with an ACK bit (active low for acknowledged) for that address. The master then continues in either transmit or receive mode (according to the read/write bit it sent), and the slave continues in its complementary mode (receive or transmit, respectively).

The address and the data bytes are sent most significant bit first. The start bit is indicated by a high-tolow transition of SDA with SCL high; the stop bit is indicated by a low-to-high transition of SDA with SCL high.

If the master wishes to write to the slave then it repeatedly sends a byte with the slave sending an ACK bit. (In this situation, the master is in master transmit mode and the slave is in slave receive mode.)

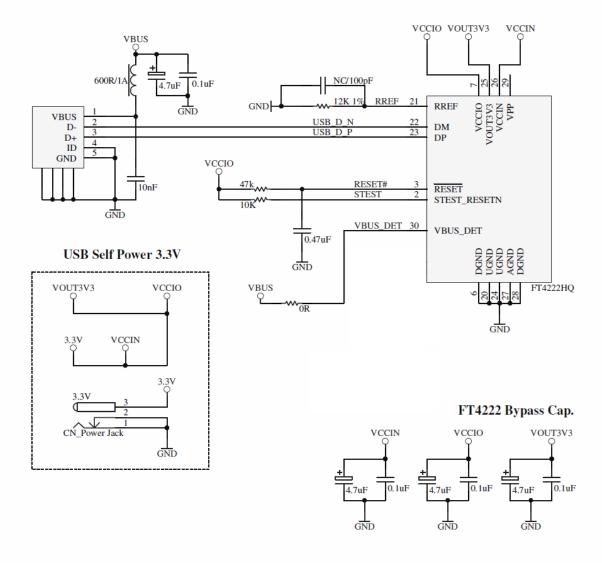

If the master wish to read from the slave then it repeatedly receives a byte from the slave, the master sends an ACK bit after every byte but the last one. (In this situation, the master is in master receive mode and the slave is in slave transmit mode.)