# TEC2200-12-074xA AC-DC CRPS Front-End Power Supply

TEC2200-12-074xA is a 2200 W Common Redundant Power Supply (CRPS) power supply that converts standard AC mains power or High Voltage DC bus voltages (HVDC) into a main output of 12 VDC for powering systems using distributed power architectures.

The power supply is hot-swappable and supports N+1 redundant architecture. The high-power density helps to improve the overall system efficiency and enhance system reliability. The full digital control facilitates remote set-up, monitoring and control.

TEC2200-12-074xA offers multiple protections including overvoltage, overtemperature, overcurrent, overpower & short circuit protection.

This power supply meets international safety standards and displays the CE-Mark for the European Low Voltage Directive (LVD).

## **Key Features & Benefits**

- 80 PLUS Titanium Efficiency

- Input Voltage Range 90 264 VAC / 180 300 VDC

- Nominal Output Voltage 12 VDC

- Standby Output 12 V<sub>SB</sub> (2.1 A)

- Output Power up to 2200 W

- Intel Standard CRPS Form Factor

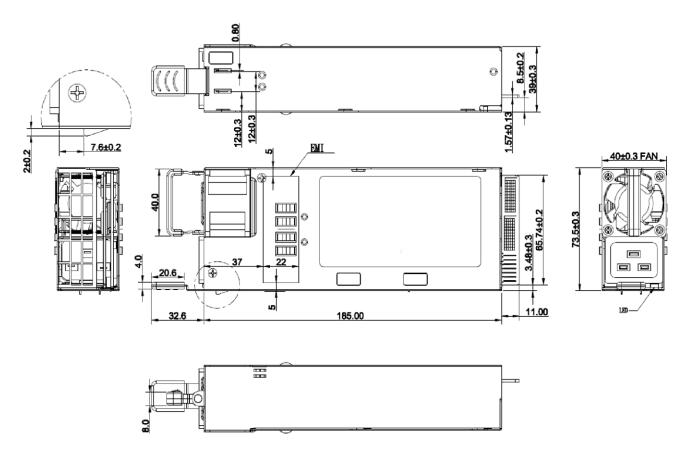

- Dimensions: 185 x 73.5 x 40 mm (7.28 x 2.89 x 1.57 in)

- High Power Density

- UL/CSA 62368-1, EN/IEC 62368-1 Certified (Pending Approval)

- Supports N+1 Redundancy, Cold Redundancy, Internal ORing

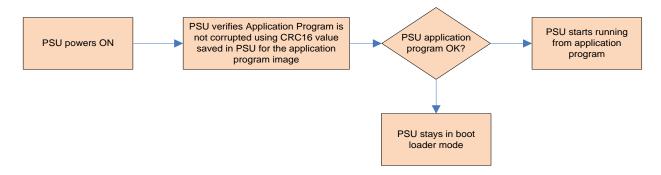

- Black Box Recorder, Bootloader

- Clockwise and Counter-Clockwise Fan Rotation

- Supports Power Management Bus Communication Protocol

## **Applications**

- Networking Switches

- Servers & Routers

- Telecommunications

## **1 ORDERING INFORMATION**

| TEC            | 2200        | -    | 12        | -    | 074     | x                       | Α     |

|----------------|-------------|------|-----------|------|---------|-------------------------|-------|

| Product Family | Power Level | Dash | V1 Output | Dash | Width   | Airflow                 | Input |

| TEC Front-Ends | 2200 W      |      | 12 V      |      | 73.5 mm | N: Normal<br>R: Reverse | A: AC |

## 2 INPUT

| PARAMETER                                   | DESCRIPTION / CONDITION                                                                                                      | MIN          | NOM     | MAX | UNIT             |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-----|------------------|

|                                             | Low Voltage AC Range (1000 W)                                                                                                | 90           | 100-127 | 140 | V <sub>RMS</sub> |

|                                             | Low Voltage Start-up                                                                                                         |              | 85 ± 5  |     | VAC              |

|                                             | Low Voltage Power Off                                                                                                        |              | 75 ± 5  |     | VAC              |

|                                             | High Voltage AC Range (2200 W)                                                                                               | 180          | 200-240 | 264 | VRMS             |

| Input Voltage Ranges*                       | High Voltage Start-up                                                                                                        |              | 175 ± 5 |     |                  |

|                                             | High Voltage Power Off                                                                                                       |              | 165 ± 5 |     |                  |

|                                             | HVDC (240 V)                                                                                                                 | 180          | 240     | 300 | VDC              |

|                                             | Start-up                                                                                                                     |              | 170 ± 5 |     | VDC              |

|                                             | Power Off                                                                                                                    |              | 160 ± 5 |     | VDC              |

| AC Line Inrush Current                      |                                                                                                                              |              |         | 50  | A <sub>pk</sub>  |

| Input Frequency                             |                                                                                                                              | 47           | 50/60   | 63  | Hz               |

|                                             | 230 VAC and 50 Hz, 10% load                                                                                                  | 0.90         |         |     |                  |

| Power Factor                                | 230 VAC and 50 Hz, 20% load                                                                                                  | 0.96         |         |     |                  |

|                                             | 230 VAC and 50 Hz, 50% load                                                                                                  | 0.98         |         |     |                  |

|                                             | 230 VAC and 50 Hz, 100% load                                                                                                 | 0.99         |         |     |                  |

|                                             | 200 / 240 VAC and 50/60 Hz, ≥ 10% load                                                                                       |              |         | 20  |                  |

|                                             | 200 / 240 VAC and 50/60 Hz, > 20% & < 30 % load                                                                              |              |         | 15  |                  |

| Current iTHD<br>(Total Harmonic Distortion) | 200 / 240 VAC and 50/60 Hz, ≥ 30 % load                                                                                      |              |         | 10  | %                |

|                                             | 200 / 240 VAC and 50/60 Hz, ≥ 50% load                                                                                       |              |         | 8   |                  |

|                                             | 200 / 240 VAC and 50/60 Hz, 100% load                                                                                        |              |         | 5   |                  |

|                                             | 230 VAC / 60 Hz, 10% load                                                                                                    | 90           |         |     | %                |

| Efficiency                                  | 230 VAC / 60 Hz, 20% load                                                                                                    | 94           |         |     | %                |

| Enciency                                    | 230 VAC / 60 Hz, 50% load                                                                                                    | 96           |         |     | %                |

|                                             | 230 VAC / 60 Hz, 100% load                                                                                                   | 93           |         |     | %                |

| Hold-up Time                                | @ 70% of max. loading                                                                                                        | 6            |         |     | ms               |

| 12V <sub>SB</sub> Hold-up Time              | @ 100% load                                                                                                                  | 70           |         |     | ms               |

|                                             | 0 to 1/2 AC cycle (nom AC voltage ranges, 50/60 Hz)<br>No loss of function or performance. (0%-60%load)                      |              | 95      |     | %                |

| AC Line Sag                                 | <ul> <li>&gt; 1 AC cycle (nom AC voltage ranges, 50/60 Hz)</li> <li>Loss of function acceptable, self-recoverable</li> </ul> | 30           |         |     | %                |

| AC Line Surge                               | Continuous (nom AC voltage ranges, 50/60 Hz)<br>No loss of function or performance                                           |              | 10      |     | %                |

|                                             | 0 to 1/2 AC cycle (mid-point of nom VAC ranges, 50/60 Hz)<br>No loss of function or performance                              |              | 30      |     | %                |

| AC Line Isolation                           | Primary to secondary; reinforced insulation (IEC 60950)                                                                      | 3000<br>4242 |         |     | VAC<br>VDC       |

\* The Brown IN/OUT Hysteresis min is 5 VAC.

1. Maximum input current at high input voltage range is measured at 200 VAC, at max load 2200 W (16 Arms)

2. AC Brown-in/out loading is 80%load; (low line & high line)

## **3 OUTPUT**

| PARAMETER                          | DESCRIPTION / CONDITION                                       | MIN    | NOM   | MAX       | UNIT             |

|------------------------------------|---------------------------------------------------------------|--------|-------|-----------|------------------|

| Output Voltage                     | Output voltage adjusted to 12.2 VDC $\pm$ 0.05 VDC @ 50% load |        | 12.2  |           | VDC              |

| Voltage Regulation Limits          | ±6%                                                           | +11.47 | +12.2 | +12.93    | VRMS             |

| Max Continuous Output Power        | Low line: 1000 W                                              |        |       | 2200      | W                |

| Output Current                     | @ 110 VAC<br>@ 220 VAC                                        | 0      |       | 82<br>178 | А                |

| Load Regulation                    |                                                               |        | ± 3   |           | %                |

| Line Regulation                    |                                                               |        | ± 1   |           | %                |

| Overshoot / Undershoot             |                                                               |        | 5     |           | %                |

| Transient Load *                   | $\Delta$ Step Load Size, 50% of Load Max, 3300 $\mu F$        |        |       | 0.5       | A/µs             |

| Capacitive Loading                 |                                                               | 3300   |       | 20000     | μF               |

| Output Ripple & Noise              | 10 Hz to 20 MHz BW                                            |        |       | 150       | mVpp             |

| +12 V <sub>SB</sub> OUTPUT         |                                                               |        |       |           |                  |

| +12 V <sub>SB</sub> Output Voltage |                                                               |        | +12.2 |           | $V_{\text{SB}}$  |

| Voltage Regulation Limits          | ± 5 %                                                         | +11.59 | +12.2 | +12.81    | V <sub>RMS</sub> |

| +12 V <sub>SB</sub> Output Current |                                                               | 0      |       | 2.1       | А                |

| Load Regulation                    |                                                               |        | ± 3   |           | %                |

| Line Regulation                    |                                                               |        | ± 1   |           | %                |

| Overshoot / Undershoot             |                                                               |        | 5     |           | %                |

| Transient Load                     | $\Delta$ Step Load Size = 1 A, 1000 $\mu$ F                   |        |       | 0.5       | A/µs             |

| Capacitive Loading                 |                                                               | 100    |       | 3100      | μF               |

| Output Ripple & Noise              | 10 Hz to 20 MHz BW                                            |        |       | 150       | mVpp             |

\* For dynamic condition +12 V min loading is 1 A

## 3.1 CRPS LOAD REQUIREMENTS

| Output               | Input voltage<br>(VAC) | Min. (A) | Max. Continuous<br>(A) | CLST Peak<br>20 sec duration<br>(A) | Pmax. app Peak<br>10 msec duration<br>(A) |

|----------------------|------------------------|----------|------------------------|-------------------------------------|-------------------------------------------|

| 12V main             | 200 – 240              | 0.0      | PSU rating (178 A)     | Rated + 6 A                         | Rated + 30 A                              |

| 12V main             | 100 – 127              | 0.0      | PSU rating (82 A)      | Rated + 6 A                         | Rated + 30 A                              |

| 12Vstby <sup>1</sup> | 100 – 240              | 0.0      | 2.1                    | 2.4                                 | NA                                        |

<sup>1</sup> The length of time 20 sec peak power can be supported, based on thermal sensor and assertion of the SMBAlert# signal. Minimum peak power duration is 20 seconds without asserting the SMBAlert# signal at maximum operating temperature.

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941 North America +1 866 513 2839

BCD.20216\_A

© 2022 Bel Fuse Inc.

## **3.2 TIMING REQUIREMENTS**

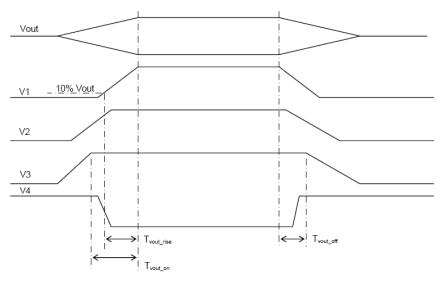

Figure 1. Signal Timing Sequence 1

#### Timing Values for Signal Timing Sequence 1:

| ITEM        | DESCRIPTION                                                                | MIN | MAX | UNITS |

|-------------|----------------------------------------------------------------------------|-----|-----|-------|

| Tvout rise  | Output voltage rise time from each main output.                            | 1   | 70  | ms    |

| T12vsb rise | Output voltage rise time for the +12VSB output.                            | 1   | 25  | ms    |

| Tvout_on    | All main outputs must be within regulation of each other within this time. |     | 50  | ms    |

| Tvout off   | All main outputs must leave regulation within this time.                   |     | 400 | ms    |

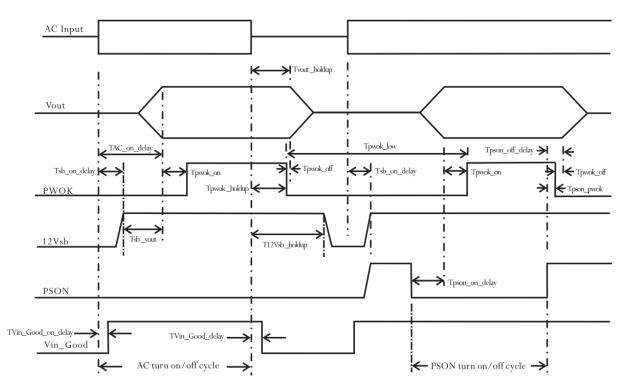

#### **Timing Values for Signal Timing Sequence 2:**

| ITEM               | DESCRIPTION                                                                                       | MIN | MAX  | UNITS |

|--------------------|---------------------------------------------------------------------------------------------------|-----|------|-------|

| Tsb_on delay       | Delay from AC being applied to 12VSB being within regulation.                                     |     | 1500 | ms    |

| Tac_on_delay       | Delay from AC being applied to all output voltages being within regulation.                       |     | 2500 | ms    |

| Tvout holdup       | Time 12V output voltage dropping to regulation after loss of AC at 70% load condition.            | 6   |      | ms    |

| Tpwok holdup       | Delay from loss of AC to desertion of PWOK at 70% load condition.                                 | 5   |      | ms    |

| Tpson_on_delay     | Delay from PSON#active to output voltages within regulation limits.                               | 5   | 400  | ms    |

| Tpson pwok         | Delay from PSON# deactivate to PWOK being deserted.                                               |     | 5    | ms    |

| Tpwok_on           | Delay from output voltages within regulation limits to PWOK asserted at turn on.                  | 100 | 500  | ms    |

| Tpwok off          | Delay from PWOK de-asserted to +12V dropping out of regulation limits.                            | 1   |      | ms    |

| Tpwok_low          | Duration of PWOK being in the deserted state during an off/on cycle using AC or the PSON# signal. | 100 |      | ms    |

| Tsb_vout           | Delay from 12 VSB being in regulation to O/Ps being in regulation at AC turn on.                  | 50  | 2000 | ms    |

| T12VSB holdup      | Time the +12VSB output voltage stays within regulation after loss of AC.                          | 70  |      | ms    |

| TVin_Good_delay    | Delay from loss of the AC to Vin_Good pull low.                                                   |     | 4    | ms    |

| TVin_Good_on_delay | Delay from AC being applied to Vin_Good being within regulation.                                  |     | 1500 | ms    |

|                    |                                                                                                   |     |      |       |

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941 North America +1 866 513 2839

© 2022 Bel Fuse Inc.

BCD.20216\_A

## **4 PROTECTION**

Protection circuits inside the power supply cause only the power supply's main outputs to shutdown. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15 sec and a PSON# cycle HIGH for 1 sec are able to reset the power supply.

## 4.1 OVER CURRENT PROTECTION (OCP)

The power supply shall have current limit to prevent the outputs from exceeding the values shown in table below. If the current limits are exceeded the power supply shall shutdown and latch off. The latch will be cleared by toggling the PSON# signal or by an AC power interruption. The power supply shall not be damaged from repeated power cycling in this condition. 12VSB will be auto-recovered after removing OCP limit.

|           |                                                                           | THRES         | HOLDS         | TIM   | IING   |

|-----------|---------------------------------------------------------------------------|---------------|---------------|-------|--------|

| PARAMETER | DESCRIPTION                                                               | MIN           | MAX           | MIN   | MAX    |

| OCP       | Slow over current protection<br>(shutdown and latch after MIN/MAX timing) | Rating + 10 A | Rating + 18 A | 20 ms | 200 ms |

| OCW       | Slow over current warning (SMBAlert#)                                     | Rating + 6 A  | Rating + 10 A | 10 ms | 15 ms  |

| OCPstby   | Stby over current protection<br>(shutdown, hiccup mode)                   | 2.5 A         | 4.0 A         | 1 ms  | 100 ms |

## 4.2 OVER VOLTAGE PROTECTION (OVP)

The power supply over voltage protection will be locally sensed. The power supply will shutdown and latch off after an over voltage condition occurs. This latch will be cleared by toggling the PSON# signal or by an AC power interruption. The values are measured at the output of the power supply's connectors. The voltage should never exceed the maximum levels when measured at the power connectors of the power supply connector during any single point of fail. The voltage should never trip any lower than the minimum levels when measured at the power connector. 12  $V_{SB}$  will be auto-recovered after removing OVP limit.

| PARAMETER                     | DESCRIPTION / CONDITION    | MIN  | NOM | MAX  | UNIT |

|-------------------------------|----------------------------|------|-----|------|------|

| Over Velters Protection (OVP) | +12 V Output               | 13.3 | 14  | 14.5 | V    |

| Over Voltage Protection (OVP) | +12 V <sub>SB</sub> Output | 13.3 | 14  | 14.5 | V    |

#### 4.3 OVER TEMPERATURE PROTECTION (OTP)

The power supply will be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature. In an OTP condition the PSU will shutdown. When the power supply temperature drops to within specified limits, the power supply will restore power automatically, while the 12  $V_{SB}$  remains always on. The OTP circuit must have built in margin such that the power supply will not oscillate on and off due to temperature recovering condition. The OTP trip level shall have a minimum of 5°C of ambient temperature margin.

#### 4.4 SHORT CIRCUIT PROTECTION (SCP)

The power supply shuts down and latches off for shorting the main outputs. 12  $V_{SB}$  is capable of being shorted indefinitely. The latch will be cleared by toggling the PSON# signal or by an AC power interruption. The power supply should not be damaged from repeated power cycling in this condition. 12  $V_{SB}$  will be auto-recovered after removing SCP limit.

## 4.5 OVER POWER PROTECTION (OPP)

The power supply shall support over power protection (OPP) level low enough to protect the power supply running in this mode for repeated 1msec durations at a 1% duty cycle. The power supply shall be stable operating at any load point from rated power up to the OPP point.

CRPS-185 Load Requirement: OPP Threshold = (Imax + 49 A) +/-50 W SMBAlert shall always assert ahead of the OPP threshold being exceeded

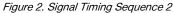

#### 4.6 CLOSED LOOP SYSTEM THROTTLING (CLST)

The power supply will always assert the SMBAlert# signal whenever temperature-monitored component in the power supply reaches a warning threshold. Upon reduction of the load within 2msec after the SMBAlert# signal is asserted if the load is reduced to less than the power supply rating; the power supply will continue to operate and not shutdown.

Figure 3. CLST Timing Requirements

#### 4.7 SMART RIDE-THROUGH (SmaRT)

The power supply will assert the SMBAlert# signal < 4 msec after AC input voltage is lost to 0 VAC.

#### **5 CONTROL**

The following sections define the input and output signals from the power supply. Signals that can be defined as low true use the following convention: Signal# = low true.

#### 5.1 DEVICE ADDRESS LOCATION (B19: A0; B20: A1)

Address Bit 0: A 10 k $\Omega$  pull-up resistor pulled to internal +3.3 V in the PSU. Address Bit 1: A 10 k $\Omega$  pull-up resistor pulled to internal +3.3 V in the PSU.

| LOCATIONS                | PSU#1                                      | PSU#2  |

|--------------------------|--------------------------------------------|--------|

| PBD addressA1/A0         | 0/0                                        | 0/1    |

| Power supply FRU device  | A0h                                        | A2h    |

| Power supply PSMI device | B0h                                        | B2h    |

| Signal type              | 10 kohm pull up resistor from +3.3 Vdd dev | vice.  |

| A1 or $A0 = low$         | A1 or A0 address bit = $0$                 |        |

| A1 or A0 = high          | A1 or A0 address bit = 1                   |        |

|                          | MIN                                        | MAX    |

| Logic level low voltage  | 0 V                                        | 0.4 V  |

| Logic level high voltage | 2.4 V                                      | 3.46 V |

#### 5.2 I2C BUS (S6: SCL; S5: SDA)

Each module shall provide SCL/SDA bus for EEPROM read/write of system. It's pull up from +3.3Vdd device by a 10K ohm resistor. System should have 1k~2k ohm pull high resistor on the SCL/SDA bus. SCL/SDA pin should be link together and closer. The SCL/SDA bus total capacitance must lower 100pF from system and PDB. The max I2C bus speed is 100 kHz and the mcu of PSU is slave device in I2C bus. The time interval of I2C command is 1ms.

Asia-Pacific Europe, Middle East +86 755 298 85888 +353 61 49 8941

st North America

+1 866 513 2839

© 2022 Bel Fuse Inc.

BCD.20216\_A

### 5.3 SMBAlert# INDICATE (Pin A22: SMBAlert#)

This is an active low signal and indicates that the power supply is experiencing a problem that the user should investigate. This shall be asserted due to Critical events or Warning events. The signal shall activate in the case of critical component temperature reached a warning threshold, general failure, over-current, over-voltage, under-voltage, failed fan. This signal may also indicate the power supply is reaching its end of life or is operating in an environment exceeding the specified limits.

This signal is to be asserted in parallel with LED turning solid Amber or blink Amber.

| SIGNAL TYPE (ACTIVE LOW)                | OPEN COLLECTOR / DRAIN OUTPUT F<br>PULL-UP TO 3.3 VSB LOCATED IN SYS |        |

|-----------------------------------------|----------------------------------------------------------------------|--------|

| Alert# = High                           | ОК                                                                   |        |

| Alert# = Low                            | Power Alert to system                                                |        |

|                                         | MIN                                                                  | MAX    |

| Logic level low voltage, Isink = 4 mA   | 0 V                                                                  | 0.4 V  |

| Logic level high voltage, Isink = 50 uA |                                                                      | 3.46 V |

| Sink current, Alert# = low              |                                                                      | 4 mA   |

| Sink current, Alert# = high             |                                                                      | 50 µA  |

## 5.4 PS-ON INPUT SIGNAL (PIN: A21: PS-ON)

The PS-ON signal is required to remotely turn on/off the power supply. PSON# is an active low signal that turns on the +12V power rail. When this signal is not pulled low by the system, or left open, the outputs (except the +12VSB) turn off. This signal is pulled to a standby voltage by a pull-up resistor internal to the power supply.

| SIGNAL TYPE                         | ACCEPTS AN OPEN COLLECTOR/DRAIN INPUT FROM THE SYSTEM.<br>PULL-UP TO 3.3VSB LOCATED IN POWER SUPPLY. |        |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------|--------|--|

| PSON# = Low                         | ON                                                                                                   |        |  |

| PSON# = High or Open                | OFF                                                                                                  |        |  |

|                                     | MIN                                                                                                  | MAX    |  |

| Logic level low (power supply ON)   | 0 V                                                                                                  | 1.0 V  |  |

| Logic level high (power supply OFF) | 2.0 V                                                                                                | 3.46 V |  |

| Source current, Vpson = low         |                                                                                                      | 4 mA   |  |

| Power off delay: Tpson_off_delay    |                                                                                                      | 5 ms   |  |

| Power up delay: Tpson_on_delay      | 5 ms                                                                                                 | 400 ms |  |

| PWOK delay: T pson_pwok             |                                                                                                      | 5 ms   |  |

#### 5.5 PWOK OUTPUT SIGNAL (PIN A25: PWOK)

PWOK is a power OK signal and will be pulled HIGH by the power supply to indicate that all the outputs are within the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power has been removed for a sufficiently long time so that power supply operation is no longer guaranteed, PWOK will be de-asserted to a LOW state. See Table: for a representation of the timing characteristics of PWOK. The start of the PWOK delay time shall be inhibited as long as any power supply output is in current limit.

| SIGNAL TYPE                                | OPEN COLLECTOR/DRAIN OUTPUT FROM POWER SUPPLY.<br>PULL-UP TO 3.3VSB LOCATED IN THE POWER SUPPLY. |        |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------|--------|--|

| PWOK = High                                | Po                                                                                               | wer OK |  |

| PWOK = Low                                 | Power Not OK                                                                                     |        |  |

|                                            | MIN                                                                                              | MAX    |  |

| Logic level low voltage, Isink = 400 uA    | 0 V                                                                                              | 0.4 V  |  |

| Logic level high voltage, Isource = 200 uA | 2.4 V                                                                                            | 3.46 V |  |

| Sink current, PWOK = low                   |                                                                                                  | 400 µA |  |

| Source current, PWOK = high                |                                                                                                  | 2 mA   |  |

| PWOK delay: Tpwok_on                       | 100 ms                                                                                           | 500 ms |  |

| PWOK rise and fall time                    |                                                                                                  | 100 μs |  |

#### 5.6 SMART ON CONTROL (PIN B22: ENABLE BY SYSTEM)

Before enabling Smart On function, make sure pin B22 (SMART ON) on output golden finger of each PSU is connected together.

#### 5.7 PRESENT# (Pin B24)

This signal is an active low type signal and is connected to the power supply's output ground internally. The mating pin of this signal in system side should have a pull-up resistor which limit the max. current 4mA to go through from this signal pin to the power supply. A Low state on this signal indicates the PSU is physically presents.

#### 5.8 Vin\_Good (Pin B25)

This signal is an output to indicate AC power is existence and is within operation range. It should act from high to low level within 2ms only for Vin drops out to zero and input voltage brown-out events. The 4ms timing is defined as Vin=0 to Vin\_Good signal low level.

| SIGNAL TYPE                              | PULL-UP 2kohm TO INTERNAL 3.3V LOCATED IN POWER SUPPLY. |                                     |  |  |  |  |

|------------------------------------------|---------------------------------------------------------|-------------------------------------|--|--|--|--|

| Vin_Good = High                          | Input voltage is                                        | Input voltage is in operating range |  |  |  |  |

| Vin_Good = Low                           | Input voltage is out of operating range                 |                                     |  |  |  |  |

|                                          | MIN                                                     | MAX                                 |  |  |  |  |

| Logic level low, Isink = 4 mA            | 0 V                                                     | 0.4 V                               |  |  |  |  |

| Logic level high, Isource = $50 \ \mu A$ | 2.0 V                                                   | 3.46 V                              |  |  |  |  |

| Sink current, Vin_Good = low             |                                                         | 4 mA                                |  |  |  |  |

| Source current, Vin_Good = high          |                                                         | 50 µA                               |  |  |  |  |

| Vin_Good rise and fall time              |                                                         | 400 µs                              |  |  |  |  |

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941 North America +1 866 513 2839

© 2022 Bel Fuse Inc.

BCD.20216\_A

## 6 FRU REQUIREMENTS

### **6.1 OVERVIEW**

The Power Management Bus features included in this specification are requirements for AC/DC golden box power supply for use in server systems. This specification is based on the Power Management Bus specifications parts I and II, revision 1.2.

### 6.2 RELATED DOCUMENTS

Power Management Bus Power System Management Protocol Specification Part I – General Requirements, Transport and Electrical Interface; Revision 1.2.

Power Management Bus Power System Management Protocol Specification Part II – Command Language; Revision 1.2. SMBus 2.0.

#### **6.3 HARDWARE CONNECTING**

The device in the power supply shall be compatible with both SMBus 2.0 'high power' specification for I2C Vdd based power and drive (for Vdd = 3.3 V). This bus shall operate at 3.3 V.

The circuits inside the power supply shall derive their power from the standby output. For redundant power supplies the device(s) shall be powered from the system side of the or'ing device. The Power Management Bus device shall be on whenever AC power is applied to the power supply or a parallel redundant power supply in the system. Only weak pull-up resistors shall be on SCL or SDA inside the power supply. The main pull-up resistors are provided by the system and may be connected to 3.3 Vsb. For the system design, the main pull-ups shall be located external to the power supply and derive their power from the standby rail.

## 6.4 DATA SPEED

The POWER MANAGEMENT BUS device in the power supply shall operate at the full 100 kbps SMBus speed and avoid using clock stretching that can slow down the bus. For example, the power supply can clock stretch while parsing a command or a power supply servicing multiple internal interrupts or NACK may require some use of clock stretching. The Power Management Bus device shall support SMBus cumulative clock low extend time (Tlow:sext) if < 25msec. This requires the device to extend the clock time no more than 25msec between START and STOP for any given message.

#### 6.5 BUS ERROR

The Power Management Bus device shall support SMBus clock-low timeout (Ttimeout). This capability requires the device to abort any transaction and drop off the bus if it detects the clock being held low for >25ms and be able to respond to new transactions 10ms later.

The device must recognize SMBus START and STOP conditions on ANY clock interval. (These are requirements of the SMBus specifications but are often missed in first-time hardware designs.) The device must not hang due to 'runt clocks', 'runt data', or other out-of-spec bus timing. This is defined as signals, logic-level glitches, setup, or hold times that are shorter than the minimums specified by the SMBus specification. The device is not required to operate normally but must return to normal operation once 'in spec' clock and data timing is again received. Note if the device 'misses' a clock from the master due to noise or other bus errors, the device must continue to accept 'in spec' clocks and re-synch with the master on the next START or STOP condition.

#### 6.6 FRU DATA FORMAT

For identification of the power supply an internal 256x8 bit EEPROM with Power Management Bus interface is used. The information in the EEPROM follows the IPMI (Platform Management FRU Information Storage Definition) guidelines Document Revision 1.1 from November 15, 1999.

## 6.7 COMMUNICATION ADDRESS

Four pins will be allocated for the FRU and Power Management Bus information on the Power Supply connector. One pin is the serial clock (SCL). The second pin is used for serial data (SDA). Two pins are for address lines

A0-A1 to indicate to the power supply's EEPROM and MCU. which position the power supply is located in the system. The SCL and SDA signals are pulled up by system, the address lines are also pulled up by system.

| A1 LOGICAL VOLTAGE | A0 LOGICAL VOLTAGE | PSU ADDRESS | FRU ADDRESS |

|--------------------|--------------------|-------------|-------------|

| 0                  | 0                  | 0xB0        | 0xA0        |

| 0                  | 1                  | 0xB2        | 0xA2        |

| 1                  | 0                  | 0xB4        | 0xA4        |

| 1                  | 1                  | 0xB6        | 0xA6        |

## 7 POWER MANAGEMENT BUS

#### 7.1 POWER MANAGEMENT BUS COMMAND TABLE

The following table shows mandatory Power Management Bus commands to be supported by the PSU.

| COMMAND  |                    | SMBUS TRAN   | NSACTION TYPE:              | NUMBER OF     |                                       |

|----------|--------------------|--------------|-----------------------------|---------------|---------------------------------------|

| CODE     | COMMAND NAME       | Writing Data | Reading Data                | DATA<br>BYTES | COMMENT                               |

| 00h      | PAGE               | Write Byte   | Read Byte                   | 1             |                                       |

| 01h      | OPERATION          | Write Byte   | Read Byte                   | 1             | 0x80 ON;<br>0x00 OFF<br>Default: 0x80 |

| 02h      | ON_OFF_CONFIG      | Write Byte   | Read Byte                   | 1             | 0x1D                                  |

| 03h      | CLEAR_FAULTS       | Send Byte    | N/A                         | 0             |                                       |

| 05h      | PAGE_PLUS_WRITE    | Block Write  | N/A                         | Variable      |                                       |

| 06h      | PAGE_PLUS_READ     | N/A          | Block Write –<br>Block Read | Variable      |                                       |

| 19h      | CAPABILITY         | N/A          | Read Byte                   | 1             | 0xB0                                  |

| 1Ah      | QUERY              | N/A          | Block Write –<br>Block Read | 1             |                                       |

| 1Bh      | SMBALERT_MASK      | Write Word   | Block Write –<br>Block Read | 2             |                                       |

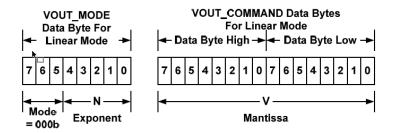

| 20h      | VOUT_MODE          |              | Read Byte                   | 1             | 0x17 (n=-9)                           |

| 21h      | VOUT_COMMAND       | Write Word   | Read Word                   | 2             |                                       |

| 30h      | COEFFICIENTS       | N/A          | Block Write –<br>Block Read | 5             | Use for Ein/Eout                      |

| 31h      | POUT_MAX           | N/A          | Read Word                   | 2             |                                       |

| 3Ah      | FAN_CONFIG_1_2     | Write Byte   | Read Byte                   | 1             | Default is Duty                       |

| 3Bh      | FAN_COMMAND_1      | Write Word   | Read Word                   | 2             |                                       |

| 4Ah      | IOUT_OC_WARN_LIMIT |              | Read Word                   | 2             |                                       |

| 51h      | OT_WARN_LIMIT      |              | Read Word                   | 2             |                                       |

| 5Dh      | IIN_OC_WARN_LIMIT  |              | Read Word                   | 2             |                                       |

| 6Ah      | POUT_OP_WARN_LIMIT |              | Read Word                   | 2             |                                       |

| 6Bh      | PIN_OP_WARN_LIMIT  |              | Read Word                   | 2             |                                       |

| 78h      | STATUS_BYTE        | Write Byte   | Read Byte                   | 1             |                                       |

| Bit 6    | OFF                |              |                             |               |                                       |

| Bit 5    | VOUT_OV_FAULT      |              |                             |               |                                       |

| Bit 4    | IOUT_OC            |              |                             |               |                                       |

| Bit 3    | VIN_UV             |              |                             |               |                                       |

| Bit 2    | TEMPERATURE        |              |                             |               |                                       |

| Bit 1    | CML                |              |                             |               |                                       |

| Bit 0    | NON OF THE ABOVE   |              |                             |               |                                       |

| 79h      | STATUS_WORD        | Write Word   | Read Word                   | 2             |                                       |

| Bit 7(H) | VOUT               |              |                             |               |                                       |

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941 North America +1 866 513 2839

11

© 2022 Bel Fuse Inc.

| Dit 6    |                                 |            |            |               |                    |

|----------|---------------------------------|------------|------------|---------------|--------------------|

| Bit 6    | IOUT/POUT                       |            |            |               |                    |

| Bit 5    | INPUT                           |            |            |               |                    |

| Bit 3    | POWER_GOOD#                     |            |            |               |                    |

| Bit 2    | FANS                            |            |            |               |                    |

| Bit 6(L) | OFF                             |            |            |               |                    |

| Bit 5    | VOUT_OV_FAULT                   |            |            |               |                    |

| Bit 4    | IOUT_OC_FAULT                   |            |            |               |                    |

| Bit 3    | VIN_UV_FAULT                    |            |            |               |                    |

| Bit 2    | TEMPERATURE                     |            |            |               |                    |

| Bit 1    | CML                             |            |            |               |                    |

| Bit 0    | NON OF THE ABOVE                |            |            |               |                    |

| 7Ah      | STATUS_VOUT                     | Write Byte | Read Byte  | 1             |                    |

| Bit 7    | VOUT_OV_FAULT                   |            |            |               |                    |

| Bit 4    | VOUT_UV_FAULT                   |            |            |               |                    |

| 7Bh      | STATUS_IOUT                     | Write Byte | Read Byte  | 1             |                    |

| Bit 7    | lout OC fault                   | ,          | ,          |               |                    |

| Bit 5    | lout OC warning                 |            |            |               |                    |

| Bit 1    | Pout OP fault                   |            |            |               |                    |

| Bit 0    | Pout OP warning                 |            |            |               |                    |

| 7Ch      | STATUS_INPUT                    | Write Byte | Read Byte  | 1             |                    |

| Bit 5    |                                 | White Dyte | nead byte  | 1             |                    |

|          | Vin UV warning                  |            |            |               |                    |

| Bit 4    | Vin UV fault                    |            |            |               |                    |

| Bit 3    | Unit off for insufficient input |            |            |               |                    |

| Bit 1    | lin over current warning        |            |            |               |                    |

| Bit 0    | Pin over power warning          |            |            |               |                    |

| 7Dh      | STATUS_TEMPERATURE              | Write Byte | Read Byte  | 1             |                    |

| Bit 7    | OT fault                        |            |            |               |                    |

| Bit 6    | OT warning                      |            |            |               |                    |

| 7Eh      | STATUS_CML                      | Write Byte | Read Byte  | 1             |                    |

| Bit 7    | Invalid COMMAND                 |            |            |               |                    |

| Bit 6    | Invalid DATA                    |            |            |               |                    |

| Bit 5    | PEC Failed                      |            |            |               |                    |

| 81h      | STATUS_FANS_1_2                 | Write Byte | Read Byte  | 1             |                    |

| Bit 7    | Fan 1 fault                     |            |            |               |                    |

| Bit 5    | Fan 1 warning                   |            |            |               |                    |

| Bit 3    | Fan1 speed overridden           |            |            |               |                    |

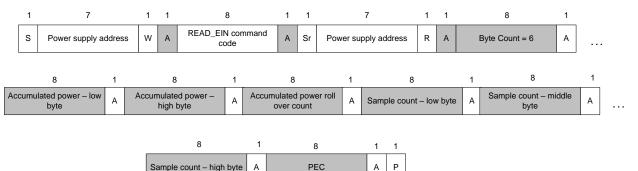

| 86h      | READ_EIN                        | N/A        | Block Read | 6             | DIRECT Data Format |

| 87h      | <br>READ_EOUT                   | N/A        | Block Read | 6             | DIRECT Data Format |

| 88h      | READ_VIN                        | N/A        | Read Word  | 2             | Linear             |

| 89h      | READ_IIN                        | N/A        | Read Word  | 2             | Linear             |

| 8Bh      | READ_VOUT                       | N/A        | Read Word  | 2             | Linear16           |

| 8Ch      | READ_IOUT                       | N/A        | Read Word  | 2             | Linear             |

| 8Dh      | READ_TEMPERATURE_1              | N/A N/A    | Read Word  | 2             | Ambient            |

|          |                                 |            |            |               |                    |

| 8Eh      | READ_TEMPERATURE_2              | N/A        | Read Word  | 2             | SR Hotspot         |

| 8Fh      | READ_TEMPERATURE_3              | N/A        | Read Word  | 2             | PFC Hotspot        |

| 90h      | READ_FAN_SPEED_1                | N/A        | Read Word  | 2             | In RPM             |

| 96h      | READ_POUT                       | N/A        | Read Word  | 2             | Linear             |

| 97h      | READ_PIN                        | N/A        | Read Word  | 2             | Linear             |

| 98h      | PMBUS_REVISION                  | N/A        | Read Byte  | 1             | 1.2                |

| 99h      | MFR_ID                          | N/A        | Block Read | Variable (3)  | "bel"              |

|          |                                 | N/A        | Block Read | Variable (16) | "TEC2200-12-074NA" |

| 9Ah      | MFR_MODEL                       | IN/A       | DIOCKTICAU | Valiable (10) | "TEC2200-12-074RA" |

| 9Ch | MFR_LOCATION                | N/A         | Block Read | Variable (8)  | "DONGGUAN"      |

|-----|-----------------------------|-------------|------------|---------------|-----------------|

| 9Dh | MFR_DATE                    | N/A         | Block Read | Variable (8)  | "YYYYMMDD"      |

| 9Eh | MFR_SERIAL                  | N/A         | Block Read | Variable (19) | Serial Number   |

| 9Fh | APP_PROFILE_SUPPORT         | N/A         | Block Read | Variable (2)  | PMBus 1.2       |

| A0h | MFR_VIN_MIN                 | N/A         | Read Word  | 2             | 90V             |

| A1h | MFR_VIN_MAX                 | N/A         | Read Word  | 2             | 264V            |

| A2h | MFR_IIN_MAX                 | N/A         | Read Word  | 2             |                 |

| A3h | MFR_PIN_MAX                 | N/A         | Read Word  | 2             |                 |

| A4h | MFR_VOUT_MIN                | N/A         | Read Word  | 2             | 11.47V          |

| A5h | MFR_VOUT_MAX                | N/A         | Read Word  | 2             | 12.93V          |

| A6h | MFR_IOUT_MAX                | N/A         | Read Word  | 2             |                 |

| A7h | MFR_POUT_MAX                | N/A         | Read Word  | 2             |                 |

| A8h | MFR_TAMBIENT_MAX            | N/A         | Read Word  | 2             |                 |

| A9h | MFR_TAMBIENT_MIN            | N/A         | Read Word  | 2             |                 |

| AAh | MFR_EFFICIENCY_LL           | N/A         | Block Read | 14            | At 20%/50%/100% |

| ABh | MFR_EFFICIENCY_HL           | N/A         | Block Read | 14            | At 20%/50%/100% |

| C0h | MFR_MAX_TEMP_1              | N/A         | Read Word  | 2             |                 |

| C1h | MFR_MAX_TEMP_2              | N/A         | Read Word  | 2             |                 |

| C2h | MFR_MAX_TEMP_3              | N/A         | Read Word  | 2             |                 |

| D0h | MFR_COLD_ REDUNDANCY_CONFIG | Write Byte  | Read Byte  | 1             |                 |

| D4h | MFR_HW_COMPATIBILITY        | N/A         | Read Word  | 2             |                 |

| D5h | MFR_FWUPLOAD_CAPABILITY     | N/A         | Read Byte  | 1             |                 |

| D6h | MFR_FWUPLOAD_MODE           | Write Byte  | Read Byte  | 1             |                 |

| D7h | MFR_FWUPLOAD                | Block Write | N/A        |               |                 |

| D8h | MFR_FWUPLOAD_STATUS         | N/A         | Read Word  | 21            |                 |

| D9h | MFR_FW_REVISION             | N/A         | Block Read | 3             |                 |

| DCh | MFR_BLACK_BOX               | N/A         | Block Read | 237           |                 |

| DDh | MFR_REAL_TIME               | Block Write | Block Read | 4             |                 |

| DEh | MFR_SYSTEM_BLACK_BOX        | Block Write | Block Read | 40            |                 |

| DFh | MFR_BLACKBOX_CONFIG         | Write Byte  | Read Byte  | 1             |                 |

| E0h | MFR_CLEAR_BLACKBOX          | Send Byte   | N/A        | 1             |                 |

Table 1. Supported Power Management Bus Command

Note: Write protocol must include PEC (Packet Error Checking).

Asia-Pacific +86 755 298 85888

Europe, Middle East +353 61 49 8941

North America +1 866 513 2839

13

BCD.20216\_A

<sup>© 2022</sup> Bel Fuse Inc.

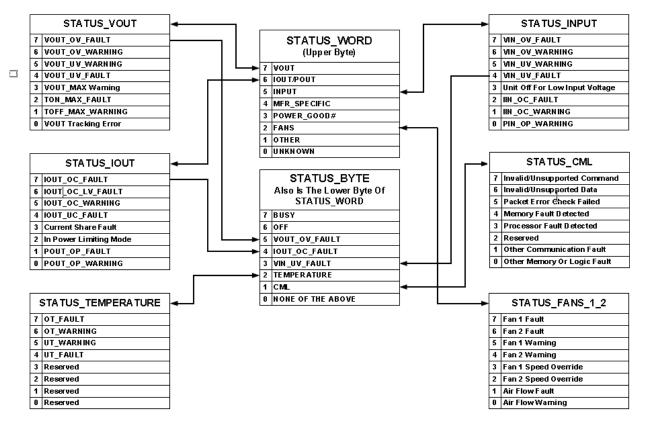

## 7.2 STATUS COMMANDS

Figure 4. Summary of The Status Registers

The following Power Management Bus STATUS commands shall be supported. All STATUS commands stated in Table Supporting PAGE instances shall support the PAGE\_PLUS\_WRITE and PAGE\_PLUS\_READ commands since they are used by both the BMC and ME. The BMC and ME refer to the two instances of the commands accessed via the

PAGE\_PLUS\_WRITE and PAGE\_ PLUS\_READ commands. The status bits shall assert whenever the event driving the status bit is present. Once a bit is asserted it shall stay asserted until cleared

The STATUS commands that are supported with the PAGE\_PLUS\_READ and PAGE\_PLUS\_W RITE commands shall still support direct access of the base STATUS\_XXX commands using the read word, write word, read byte, and write byte protocols.

STATUS\_FAN\_1\_2 command is only accessed by the system BMC. It uses the standard read byte protocol to read status and write byte protocol to clear bits.

The STATUS events are also used to control the SMBAlert# signal. The new SMBALERT\_MASK command is used to define which status event controls the SMBAlert# signal. Default values for these mask bits are shown in the table below.

| POWER MANAGEMENT<br>BUS COMMAND | BIT<br>LOCATION | PSU STATE WHEN BIT IS<br>ASSERTED ('1') | INSTANCES<br>NO PAGE'ING2<br>PAGE 00H = BMC<br>PAGE 01H = ME | SMBALERT_MASK DEFAULTS<br>FOR EACH OF THE THREE<br>INSTANCES (NO PAGE, PAGE 00H,<br>PAGE 01H)<br>0 = CAUSES ASSERTION OF<br>SMBALERT#<br>1 = DOES NOT CAUSE<br>ASSERTION OF |

|---------------------------------|-----------------|-----------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                 |                                         |                                                              | SMBALERT#                                                                                                                                                                   |

| STATUS_WORD                     |                 |                                         | No PAGE, 00h, 01h                                            |                                                                                                                                                                             |

| OFF                             | 6 (lower)       | OFF                                     |                                                              | NA                                                                                                                                                                          |

| IOUT_OC_FAULT                   | 4 (lower)       | Refer to STATUS_IOUT                    |                                                              | NA                                                                                                                                                                          |

| VIN_UV_FAULT                    | 3 (lower)       | Refer to STATUS_INPUT                   |                                                              | NA                                                                                                                                                                          |

| TEMPERATURE                     | 2 (lower)       | Refer to STATUS_TEMPERATURE             |                                                              | NA                                                                                                                                                                          |

| CML                             | 1 (lower)       | ON                                      |                                                              | NA                                                                                                                                                                          |

| VOUT                            | 7 (upper)       | Refer to STATUS_VOUT                    |                                                              | NA                                                                                                                                                                          |

| IOUT/POUT                       | 6 (upper)       | Refer to STATUS_IOUT                    |                                                              | NA                                                                                                                                                                          |

| INPUT                           | 5 (upper)       | Refer to STATUS_INPUT                   |                                                              | NA                                                                                                                                                                          |

| FANS                            | 2 (upper)       | Refer to STATUS_FANS                    |                                                              | NA                                                                                                                                                                          |

| STATUS_VOUT                     |                 |                                         | No PAGE'ing                                                  |                                                                                                                                                                             |

| VOUT_OV_FAULT                   | 7               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| VOUT_UV_FAULT                   | 4               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| STATUS_IOUT                     |                 |                                         | No PAGE'ing, 00h,01h                                         |                                                                                                                                                                             |

| IOUT_OC_FAULT                   | 7               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| IOUT_OC_WARNING                 | 5               | ON                                      |                                                              | 1, 1, 0                                                                                                                                                                     |

| POUT_OP_FAULT                   | 1               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| POUT_OP_WARNING                 | 0               | ON                                      |                                                              | 1, 1, 1                                                                                                                                                                     |

| STATUS_INPUT                    |                 |                                         | No PAGE'ing, 00h,01h                                         |                                                                                                                                                                             |

| VIN_UV_WARNING                  | 5               | ON                                      |                                                              | 1, 1, 1                                                                                                                                                                     |

| VIN_UV_FAULT                    | 4               | OFF                                     |                                                              | 1, 1, 0                                                                                                                                                                     |

| Unit off for low input voltage  | 3               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| IIN_OC_WARNING                  | 1               | ON                                      |                                                              | 1, 1, 1                                                                                                                                                                     |

| PIN_OP_WARNING                  | 0               | ON                                      |                                                              | 1, 1, 1                                                                                                                                                                     |

| STATUS_TEMPERATURE              |                 |                                         | No PAGE'ing, 00h,01h                                         |                                                                                                                                                                             |

| OT_FAULT                        | 7               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| OT_WARNING                      | 6               | ON                                      |                                                              | 1, 1, 0                                                                                                                                                                     |

| STATUS_FANS_1_2                 |                 |                                         | No PAGE'ing                                                  |                                                                                                                                                                             |

| Fan 1 fault                     | 7               | OFF                                     |                                                              | 1, 1, 1                                                                                                                                                                     |

| Fan 1 warning                   | 5               | ON                                      |                                                              | 1, 1, 1                                                                                                                                                                     |

|                                 |                 |                                         |                                                              |                                                                                                                                                                             |

Table 2. Power Management Bus STATUS Commands Summary

1. The Vin Fault bit in STATUS\_INPUT shall get asserted if the input power has dropped below the PSU's operating range for any duration of time; even if the PSU continues to operate normally through a momentary input dropout event.

2. 'No PAGE' is the standard STATUS\_ commands accessed directly without using the PAGE\_PLUS commands.

3. All fans in the PSU shall be OR'ed into a single fan status bit for fault and warning conditions.

Asia-Pacific +86 755 298 85888 Europe, Middle East +353 61 49 8941 North America +1 866 513 2839

BCD.20216\_A

© 2022 Bel Fuse Inc.

### 7.3 POWER MANAGEMENT BUS TEMPERATURE READ COMMANDS

The following temperature read commands as documented by the Power Management Bus specification Part II version 1.2 should be supported.

READ\_TEMPERATURE\_1(8Dh), should provide the PSU inlet temperature.

READ\_TEMPERATURE\_2(8Eh), should provide the temperature of the SR heat sink in the PSU.

READ\_TEMPERATURE\_3(8Fh), should provide the temperature of the PFC heat sink in the PSU.

#### 7.4 PAGE (00h)

Setting a PAGE value of FFh is used to clear all status bits in all PAGEs with the CLEAR\_FAULT command.

#### 7.5 OPERATION (01h)

The OPERTION command is used to configure the operational state of the converter, in conjunction with input from the CONTROL pin. The OPERATION command is used to turn the Power Management Bus device output on and off. Bit [7] controls whether the Power Management Bus device output is on or off.

If Bit [7] is cleared (equals 0) then the output is off. If Bit [7] is set (equals 1), then the output is on.

#### 7.6 ON\_OFF\_CONFIG (02h)

The ON\_OFF\_CONFIG command configures the combination of CONTROL pin input and serial bus commands needed to turn the unit on and off. This includes how the unit responds when power is applied.

The default response for any Power Management Bus device is specified by the device manufacturer. The default value is 0x1D.

X = don't care

HW = turn-on/off by control pin

HI = control pin active high turn-on power

LO = control pin active low turn-on power

SW = turn-on/off by operation command

| SETTING<br>TYPE | BIT 7~5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | DATA<br>VALUE | DESCRIPTION       | SUPPORTED |

|-----------------|---------|-------|-------|-------|-------|-------|---------------|-------------------|-----------|

| 1               | 0       | 0     | Х     | Х     | Х     | 1     | 0x01          | If AC ok, turn-on | YES       |

| 2               | 0       | 1     | 0     | 1     | 0     | 1     | 0x15          | HW + LO           | YES       |

| 3               | 0       | 1     | 1     | 0     | Х     | 1     | 0x19          | SW                | YES       |

| 4               | 0       | 1     | 1     | 1     | 0     | 1     | 0x1D          | HW + LO + SW      | YES       |

Table 3. ON\_OFF\_CONFIG Data Byte

### 7.7 CLEAR\_FAULTS COMMAND (03h)

The CLEAR\_FAULTS command is used to clear any fault bits that have been set. This command clears all bits in all status registers simultaneously. At the same time, the device negates (clears, releases) its SMBALERT# signal output if the device is asserting the SMBALERT# signal.

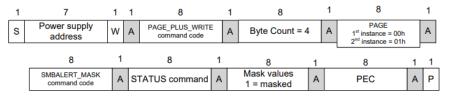

## 7.8 PAGE\_PLUS\_WRITE / PAGE\_PLUS\_READ COMMANDS (05h/06h)

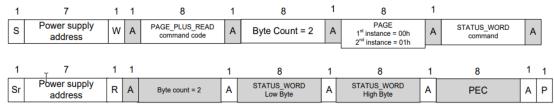

The new PAGE\_PLUS\_WRITE and PAGE\_PLUS\_READ commands are used with the STATUS\_WORD, STATUS\_INPUT, STATUS\_TEMPERATURE, STATUS\_IOUT, STATUS\_VOUT, and STATUS\_CML to create two instances of the same command. Each instance is set by the same events but cleared by their own master in the system. The instances at PAGE 00h are controlled by the system BMC and the instances at PAGE 01h are controlled by the system ME. Below are the protocols used to read and clear the STATUS\_ commands using the PAGE\_PLUS\_WRITE and PAGE\_PLUS\_READ commands.

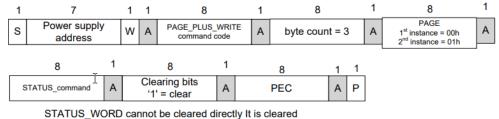

#### Reading STATUS\_WORD

Block Write - Block Read Process Call with PEC

Reading STATUS\_TEMPERATURE, STATUS\_IOUT, STATUS\_INPUT, STATUS\_CML Block Write – Block Read Process Call with PEC

b

Figure 5. Reading STATUS commands with PAGE\_PLUS\_READ

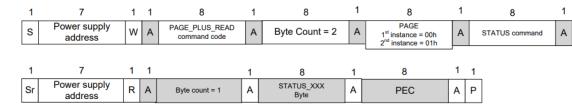

Clearing STATUS commands (write '1' to clear a bit) STATUS\_TEMPERATURE, STATUS\_IOUT, STATUS\_INPUT, STATUS\_CML Block Write with PEC

based on lower level status commands

Figure 6. Clearing STATUS commands using PAGE\_PLUS\_WRITE

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941

© 2022 Bel Fuse Inc.

North America +1 866 513 2839

## 7.9 CAPABILITY (19h)

This command provides a way for a host system to determine some key capabilities of a Power Management Bus device. There is one data byte formatted as shown in table below. This command is read only.

| BITS | DESCRIPTION           | VALUE | MEANING                                                                                            |

|------|-----------------------|-------|----------------------------------------------------------------------------------------------------|

| 7    | Packet Error Checking | 0     | Packet Error Checking not supported                                                                |

| /    | Packet Error Checking | 1     | Packet Error Checking is supported                                                                 |

|      |                       | 00    | Maximum supported bus speed is 100 kHz                                                             |

| 0.5  | Maximum Due Creed     | 01    | Maximum supported bus speed is 400 kHz                                                             |

| 6:5  | Maximum Bus Speed     | 10    | Reserved                                                                                           |

|      |                       | 11    | Reserved                                                                                           |

| 4    | SMBALERT#             | 0     | The device does not have a SMBALERT# pin and<br>does not support the SMBus Alert Response protocol |

| 4    | SWIDALEN I#           | 1     | The device does have a SMBALERT# pin and does<br>support the SMBus Alert Response protocol         |

| 3:0  | Reserved              | Х     | Reserved                                                                                           |

Table 4. CAPABILITY COMMAND Data Byte Format

### 7.10 QUERY (1Ah)

The QUERY command is used to ask a Power Management Bus device if it supports a given command, and if so, what data formats it supports for that command. This command uses the Block Write-Block Read Process Call described in the SMBus specification.

| BITS | VALUE | MEANING                                                                                          |

|------|-------|--------------------------------------------------------------------------------------------------|

| 7    | 1     | Command is supported                                                                             |

| 1    | 0     | Command is not supported                                                                         |

| 6    | 1     | Command is supported for write                                                                   |

| 0    | 0     | Command is not supported for write                                                               |

| r.   | 1     | Command is supported for read                                                                    |

| 5    | 0     | Command is not supported for read                                                                |

|      | 000   | Linear Data Format used                                                                          |

|      | 001   | 16 bit signed number                                                                             |

|      | 010   | Reserved                                                                                         |

|      | 011   | Direct Mode Format used                                                                          |

| 4:2  | 100   | 8 bit unsigned number                                                                            |

|      | 101   | VID Mode Format used                                                                             |

|      | 110   | Manufacturer specific format used                                                                |

|      | 111   | Command does not return numeric data. This is also used for commands that return blocks of data. |

| 1:0  | XX    | Reserved for future use                                                                          |

|      |       |                                                                                                  |

Table 5. QUERY Command Returned Data Byte Format

If bit [7] is zero, then the rest of the bits are "don't care".

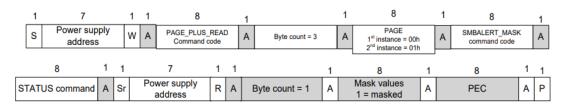

#### 7.11 SMBALERT\_MASK (1Bh)

This allows the system to mask events from asserting the SMBAlert# signal and to read back this information from the PSU. SMBALERT\_MASK command can be used with any of the supported STATUS events. The events are masked from asserting SMBAlert# by writing a '1' to the associated STATUS bits. The SMBALERT\_MASK command is used in conjunction with the PAGE\_PLUS command and STATUS\_ commands. It is not supported for masking the Non-PAGE'd STATUS\_ commands. Below are the protocols.

Figure 7. PAGE\_PLUS\_READ command.

Writing mask values using PAGE\_PLUS Block Write with PEC

STATUS\_WORD is not used with SMBALERT\_MASK. Only the 'root' event bits are used to control the SMBAlert signal

Figure 8. PAGE\_PLUS\_WRITE command.

### 7.12 COEFFICIENT (30h)

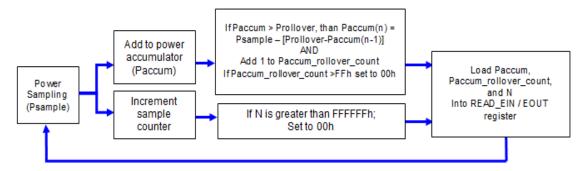

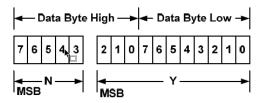

The power supply shall support the Power Management Bus COEFFICIENT command. The system shall use this to read the values of m, b, and R used to determine READ\_EIN and READ\_EOUT accumulated power values.

| COMMAND   |             |                  |        | COEFFIC       | IENTS | SUPPORT      |     | Μ          | В     | R   |

|-----------|-------------|------------------|--------|---------------|-------|--------------|-----|------------|-------|-----|

| READ_EIN  |             |                  |        |               | Yes   |              |     | 01h        | 00h   | 00h |

| READ_EOUT |             |                  |        |               | Yes   |              |     | 01h        | 00h   | 00h |

|           |             |                  |        |               |       |              |     |            |       |     |

| 1         | 7           | ' 1              | 1      | 8             | 1     | 8            | 1   |            |       |     |

| s         | SLA<br>ADDF |                  |        | EFFICIENTS    | A BY  | TE COUNT = 2 | Α   |            |       |     |

|           |             | 8                | 1      | 8             | 1     |              |     |            |       |     |

|           | C           | OMMAND           | A 01   | h (READ COEF  | F)    |              |     |            |       |     |

|           |             | CODE             | 00   1 | h (WRITE COEF |       | ••           |     |            |       |     |

|           | 1           | 7                | 11     | 8             | 1     | 8            | 1   | 8          | 1     |     |

|           | S<br>r      | SLAVE<br>ADDRESS | RA     | BYTE COUNT    | =5 A  | m: Low Byte  | e A | m: High By | /te A | •   |

|           |             | 8                | 1      | 8             | 1     | 8            | 1   | 8          | 1 1   |     |

|           | b:          | Low Byte         | A      | b: High Byte  | A     | R: One Byte  | A   | PEC        | A P   |     |

Figure 9. Retrieving Coefficients Using PEC

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941

© 2022 Bel Fuse Inc.

North America +1 866 513 2839

19

BCD.20216 A

## 7.13 FAN\_CONFIG\_1\_2 (3Ah)

The FAN\_CONFIG\_1\_2 command is used to define the presence of a fan and the method it is controlled (by duty cycle or RPM).

The first of the configuration tells the Power Management Bus device whether or not a fan associated with position 1 (or 2) is installed. Any combination of fan installation is permitted.

The second part of the configuration tells the device whether the fan speed commands are in RPM or PWM duty cycle (in percent). These settings do not have to be the same for Fan 1 and Fan 2.

The third part of the configuration data tells the Power Management Bus device the number of tachometer pulses per revolution each fan provides. This information is needed for commanding and reporting fan speed in RPM. Two bits are provided for each fan. These settings do not have to be the same for Fan 1 and Fan 2. The binary values of these bits map to pulses per revolution as follows:

- 00b = 1 pulse per revolution,

- 01b = 2 pulses per revolution,

- 10b = 3 pulses per revolution,

- 11b = 4 pulses per revolution.

This command has one data byte formatted as follows:

| BITS | VALUE    | MEANING                                |

|------|----------|----------------------------------------|